# 起動素子付き低待機電力対応電源 IC

丸山 宏志(まるやま ひろし)

城山 博伸(しろやま ひろのぶ)

園部 孝二(そのべ こうじ)

## 1 まえがき

近年,地球温暖化が世界的な問題としてクローズアップされ,電気製品全般での省エネルギー化が重要となっている。特に常時コンセントに接続されるテレビ,AV製品,OA機器,ノートパソコンのACアダプタなどでは実際に使用している時間より,使用されずに待機状態となっている時間の方が圧倒的に長いのが実態であり,全体的にみれば待機時に消費する電力の方が大きな比率を占めている。

このため待機電力の低減に各メーカーの努力が続けられ, 現在では,製品によって待機電力300mW以下,100mW 以下といった仕様の電源設計が要求される場合が多くなっ ている。

富士電機では商用交流電源(100 V,240 V)を直流電源に変換する AC-DC コンバータ用の制御 IC として,低消費電力化に有効な高耐圧 CMOS (Complementary Metal Oxide Semiconductor)プロセスを用いた製品を開発してきた。

今回は,さらに低待機電力対応の機能を強化した8ピンのカレントモードPWM(Pulse Width Modulation)制御IC「FA5506P/N」シリーズを開発したので,その概要を紹介する。

### 2 製品の概要

# 2.1 特 徵

富士電機では,30 V 耐圧の CMOS プロセスを使用し, 外付けのパワー MOSFET (Metal Oxide Semiconductor Field Effect Transistor)を駆動するタイプの AC-DC 電 源制御 IC を系列化してきた。

今回の開発品では,待機電力対応として500 V 耐圧の起動素子を内蔵し,また軽負荷時に発振周波数を下げる機能を取り入れている。

パッケージ外形は DIP ( Dual Inline Package ) と SOP (Small Outline Package ) の 2 種類を用意し,ピン配置は,8 ピンに高圧系の起動素子 ( VH ) 端子を設定し,7 ピン

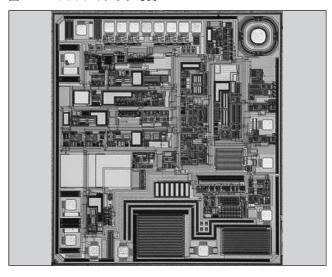

を未接続(NC)端子にして高電圧対策としている。 図1に製品の外観,図2にチップ写真を示す。

IC の主な特徴は以下のとおりである。

(1) 500 V 耐圧の JFET (Junction Field Effect Transistor)を内蔵し、IC 起動時は VH 端子から VCC 端子への充電電流を供給し、スイッチング動作状態になれば、高圧系からの起動電流をオフして損失を低減する。

起動時:3 mA(電源入力電圧 $V_{CC} = 0 \text{ V}) \sim 250 \,\mu\text{A}(V_{CC} = 15 \text{ V})$

図1 製品の外観

図 2 FA5506 のチップ写真

丸山 宏志

スイッチング電源制御 IC の開発 に従事。現在,松本工場 IC 第一 開発部。

城山 博伸

スイッチング電源制御 IC の開発 に従事。現在,松本工場 IC 第一 開発部。

園部 孝二

スイッチング電源制御 IC の開発 に従事。現在,松本工場 IC 第一 開発部。 動作時:10 uA

(2) FB 端子電圧(二次側からのフィードバック電圧)で 軽負荷時を判定し,発振周波数を異音防止・リプル対策 のためリニアに低下させることで,電源のスイッチング 損失を低減させる。

最低発振周波数 = 約 1.5 kHz

(3) 通常動作時の発振周波数は,今回の開発品では内部で 設定され外付け部品での調整はできないため,発振周波 数の違う3機種を系列化した。最大オンデューティは 80%に設定している。

FA5506: 130 kHz , FA5507: 100 kHz , FA5508: 60 kHz (4) VCC 端子はヒステリシス特性を持つ低電圧誤動作防 止(UVLO: Under Voltage Lock-Out)回路を内蔵し

14.8 V オン/9 V オフ

ている。

- (5) IS 端子は外部 MOSFET の電流をモニタする端子で , 最大入力レベルは 500 mV である。オン時のノイズ誤動 作を防止するためブランキング時間を 400 ns に設定し ている。

- (6) 過負荷, VCC 端子の過電圧, ラッチ遮断, ソフトスタートなど各種保護機能を内蔵している。

#### 2.2 起動回路

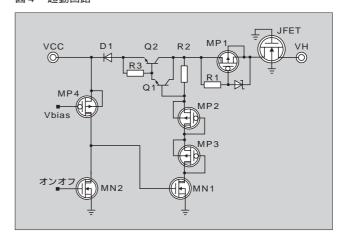

VH 端子から接続される JFET は , AC 入力を整流した 高圧ラインから直接接続される。このドレイン部分が 500 V 耐圧構造の素子である。この JFET のピンチオフ電圧 は 25 V となっているため , JFET のソースはこの電圧以 上には上昇しないのが特徴である。

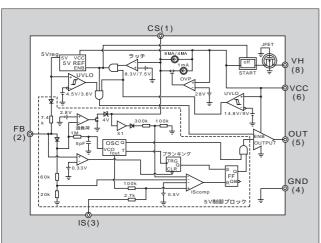

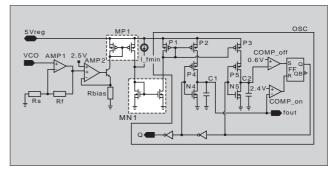

図3にIC全体のブロック図を,図4に起動回路部分を示す。JFETから電流調整用のpチャネル MOS(MP1)を通してダーリントン接続のnpnトランジスタ(Q1,Q2)が接続される。この部分が起動回路のスイッチ動作をする。

起動時はオンオフ信号が H レベルとなり MN2 はオン , MN1 はオフとなる。そのため抵抗 R2 を通して npn トランジスタ Q1 にベース電流が流れ npn トランジスタはオンとなり VCC 側へ電流が供給される。

#### 図3 回路ブロック図

VCC 端子電圧が上昇し,スイッチング動作状態の場合は,オンオフ信号が L レベルとなり,MN1 をオン状態にする。このときは,Q1 のベース電流を MP2,MP3,MN1 側へ吸い込み npn トランジスタをオフさせて,VCC 端子への供給をカットする。このとき抵抗 R2 は約 2 M の大きな抵抗値を持つため,VH 端子からの流入電流は 10 µA 程度に抑えられる。

#### 2.3 周波数低減回路

図3でFB端子からダイオードを通した電圧レベルが抵抗を通してISコンパレータ(IScomp)に入力されるとともに、1M 、5pFのフィルタを通して発振器(OSC)に入力される。この発振器内部の回路を図5に示す。

発振器では VCO 入力の電圧をアンプ (AMP1)で増幅 し,FB 端子電圧が 1 V のときに AMP1 の出力が 2.5 V に なるように設定されている。 AMP2 は,AMP1 出力と 2.5 V の低い方の電圧をバイアス抵抗 (Rbias) に発生させ,このとき流れる電流 ( $I_{\text{bias}}$ ) が発振器の周波数可変をコントロールする。

また,カレントミラー回路(MP1)で Ibias と同じ電流値の電流源を作り,さらに定電流源(I\_fmin)で示した発振周波数で 1.5 kHz に相当する分の電流を加算したものを,カレントミラー回路(MN1)に流し,発振器(OSC)のタイミングコンデンサの充電電流として供給する。

このため、FB端子の電圧が低下した場合の発振周波数はFB>1Vでは通常の発振周波数,FB<1Vでリニア

図4 起動回路

図5 周波数可変回路(発振器)

に周波数は低下し、最後は 1.5 kHz まで低下しそのまま維持される。

発振器は,オン期間用とオフ期間用の2系統の充放電回路をフリップフロップを使って交互に切り換えることで動作し,コンパレータのレベルを,4:1に設定することで最大デューティを80%に設定している。

#### 3 従来 IC との電源回路の比較

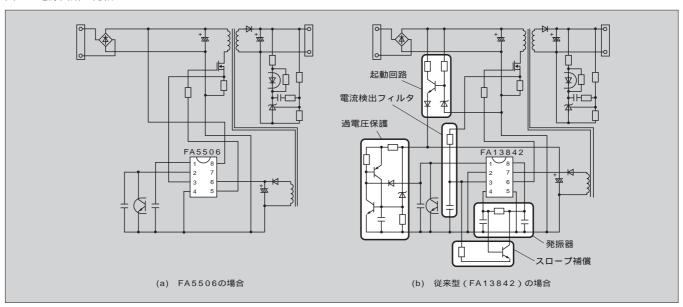

FA5506 は、従来外付け回路で構成していた起動回路や過電圧保護回路など、多くの機能を IC 内部に取り込んでいる。FA5506を使用して、一般的な電源回路を構成した場合の回路図と、これに対し代表的な従来型の電流モード制御 IC である FA13842を使用して、ほぼ同じ機能を実現した場合の回路図を図6に示す。従来型の回路図の中で、太線で囲った部分が今回 FA5506 に取り込んだ部分である。両者を比較して分かるように、FA5506を使用した場合、IC 周辺の回路を非常にシンプルに構成できる。実際、両者の回路図を比較すると、19点の部品が削減できている。この結果、IC 周辺部分の省スペース化に寄与し、電源セットの小型化にも効果が期待できる。

#### 4 電源回路への応用

#### 4.1 評価用電源

この IC を使った場合の電源回路としての特性を確認するため,実際に電源を作成し,その特性を確認した。

作成した電源の主な仕様は以下のとおりである。

- (1) 入力電圧: AC80 ~ 264 V, 50/60 Hz

- (2) 出力: DC5V, 25W

- (3) 保護機能:過負荷ラッチ,過電圧ラッチ,過電流制限

- (4) 使用 IC: FA5506(定格時発振周波数:130 kHz)

#### 4.2 軽負荷時周波数低減機能

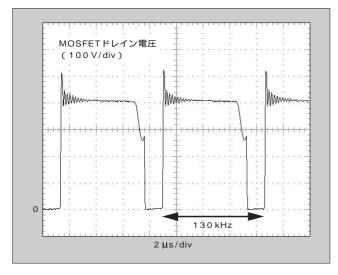

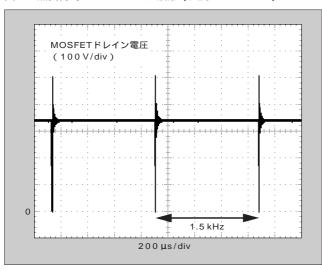

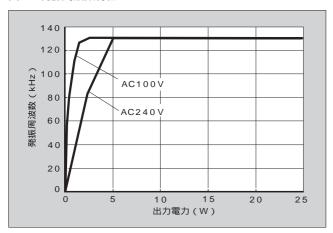

定格負荷時のスイッチング波形を図7に,無負荷の場合を図8に示す。定格負荷時には130kHzで動作しているが,無負荷時には発振周波数が低下し,約1.5kHzで動作していることが分かる。また,出力電力と発振周波数の関係を図9に示す。軽負荷になると発振周波数が徐々に低下している様子が分かる。

#### 4.3 軽負荷時の効率改善

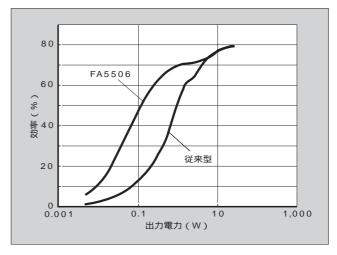

軽負荷時の効率改善効果を確認するため、従来型の IC を同じ評価用電源に搭載し、特性の比較を行った。

比較に使用したICは,起動回路および周波数低減機能を内蔵していないが,その他の特性はほぼ同等のものである。また起動回路としては,一般的に使用される抵抗のみとした。このため従来のICの場合には,ICが起動した後も常時損失が発生している。

入力が AC 240 V の場合の効率特性を図10に示す。出力電力が大きい部分では、どちらの IC も同じ発振周波数で動作しており、また起動回路で発生する損失も出力電力に比べ十分小さいため、効率にはほとんど差が見られない。

これに対し出力電力が小さくなると, FA5506 の場合, 効率が大きく改善しており,最大で約40%の効率改善を実現できている。これには大きく二つの要因が考えられる。

一つは,FA5506の場合,軽負荷時にスイッチング周波数が低下することにより,スイッチングロスが削減できていることが挙げられる。

もう一つは,起動回路の効果である。従来の IC では,起動回路として抵抗を用いた。この抵抗で発生する損失は比較的小さいものではあるが,軽負荷時にはこの損失の比率が大きくなり無視できなくなってくる。これに対し FA 5506 では,IC が動作している間はこの起動回路で発生している損失をほぼゼロとすることができるため,効率を改

#### 図7 定格負荷時のスイッチング波形 (入力 AC 240 V)

図8 無負荷時のスイッチング波形 (入力 AC 240 V)

図 9 発振周波数特性

善することができた。

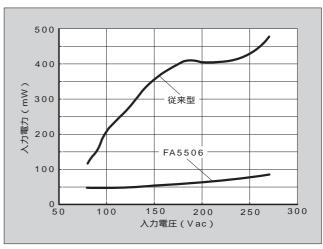

# 4.4 無負荷時の入力電力

無負荷時の入力電力の比較を行った。電源回路での無負荷の状態は、例えば AC アダプタをコンセントに差し込ん

図 10 効率特性(入力 AC 240 V)

図 11 無負荷時の入力電力

だまま,これを利用するセット側を動作させていないような場合に見られる。つまり,無負荷時の入力電力はすべて損失となり,省エネルギーの観点からは,この無負荷時の入力電力を削減することも大きなポイントとなる。

結果を図11に示す。ほぼ全入力電圧範囲で 70 %以上, 最大で約85 %の損失を削減できている。この結果,無負 荷時の入力電力をAC100 V の場合には48 mW, AC240 V の場合には75 mW に抑えることができ,全入力電圧範 囲で無負荷時の入力電力を100 mW 以下に収めることが できた。

## 5 あとがき

起動素子付きの低待機電力対応電源 IC について紹介した。この分野は今後もさらに低消費電力化の要求が厳しくなってくることが予想されるため,さらなる機能強化・使いやすさを追求した製品を開発していく所存である。

# 参考文献

(1) 丸山宏志 . 軽負荷時省電力機能付 PWM 制御 IC . 富士時報 . vol.73 , no.8 , 2000 , p.427-431 .

\*本誌に記載されている会社名および製品名は、それぞれの会社が所有する 商標または登録商標である場合があります。