## ディスクリートIGBT

### Application Manual

注意

1. この資料の内容(製品の仕様、特性、データ、材料、構造など)は2025年12月現在のものです。この内容は製品の仕様変更のため、または他の理由により事前の予告なく変更されることがあります。この資料に記載されている製品を使用する場合には、その製品の最新版の仕様書を入手して、データを確認してください。

2. 本資料に記載してある応用例は富士電機製品を使用した代表的な応用例を説明するものであり、本資料によって工業所有権、その他権利の実施に対する保証または実施権の許諾を行うものではありません。

3. 富士電機は絶えず製品の品質と信頼性の向上に努めています。しかし、半導体製品は故障が発生したり、誤動作する場合があります。富士電機製半導体製品の故障または誤動作が、結果として人身事故、火災等による財産に対する損害や、社会的な損害を起こさないように冗長設計、延焼防止設計、誤動作防止設計などの安全確保をお客様の責任において行ってください。

4. 本資料に記載している製品は、普通の信頼度が要求される下記のような電子機器や電気機器に使用されることを意図して造られています。

- ・コンピュータ・OA機器・通信機器(端末)・計測機器・工作機械

- ・オーディオビジュアル機器・家庭用電気製品・パーソナル機器・産業用ロボットなど

5. 本仕様書に記載されている製品は、人命に関わるような状況下で使用される機器あるいはシステムに用いられる事を目的として設計・製造されたものではありません。以下に示す機器あるいはシステムへの適用に関し、富士電機は一切の責任を負いません。

- ・幹線用通信機器・交通信号機・医療機器

- ・ガス警報器および遮断機・防災/防犯装置・安全確保のための各種装置

6. 極めて高い信頼度を要求される下記のような機器および戦略物資に該当する機器には、本仕様書に記載の製品を使用しないでください。

- ・車両機器(自動車、鉄道、船舶など)・宇宙機器・航空機搭載用機器

- ・原子力制御機器・海底中継機器

7. 本資料の一部または全部の転載複製については、文書による弊社の承諾が必要です。

8. 本資料の内容にご不明の点がありましたら、製品を使用する前に富士電機(株)または、その販売店へ質問してください。本注意書きの指示に従わないために生じたいかなる損害も富士電機(株)とその販売店は責任を負うものではありません。

## 第5章 保護回路設計方法

|              |     |

|--------------|-----|

| 1. 短絡(過電流)保護 | 5-2 |

| 2. 過電圧保護     | 5-8 |

本章では、ディスクリートIGBTの保護回路設計方法について説明します。

## 1. 短絡(過電流)保護

### 1.1 短絡耐量について

装置が何らかの異常により短絡状態になるとIGBTのコレクタ電流 $I_C$ が増加し、所定の値を超えるとC-E間電圧 $V_{CE}$ が急増します。この特性により、短絡時の $I_C$ を一定の値以下に抑制しますが、IGBTに高電圧・大電流が印加された状態になり、この状態が続くと破壊に至ります。IGBTがこの状態を非破壊で耐え得る時間を短絡耐量と言います。

ディスクリートIGBT XSシリーズでは短絡耐量とトレードオフの関係にある低スイッチング損失と低飽和電圧に特化した設計にしており、短絡耐量の保証をしていません。そのため、短絡が想定される回路には、XSシリーズを使用しないでください。

アーム短絡と出力短絡についての考え方を、以下に説明します。

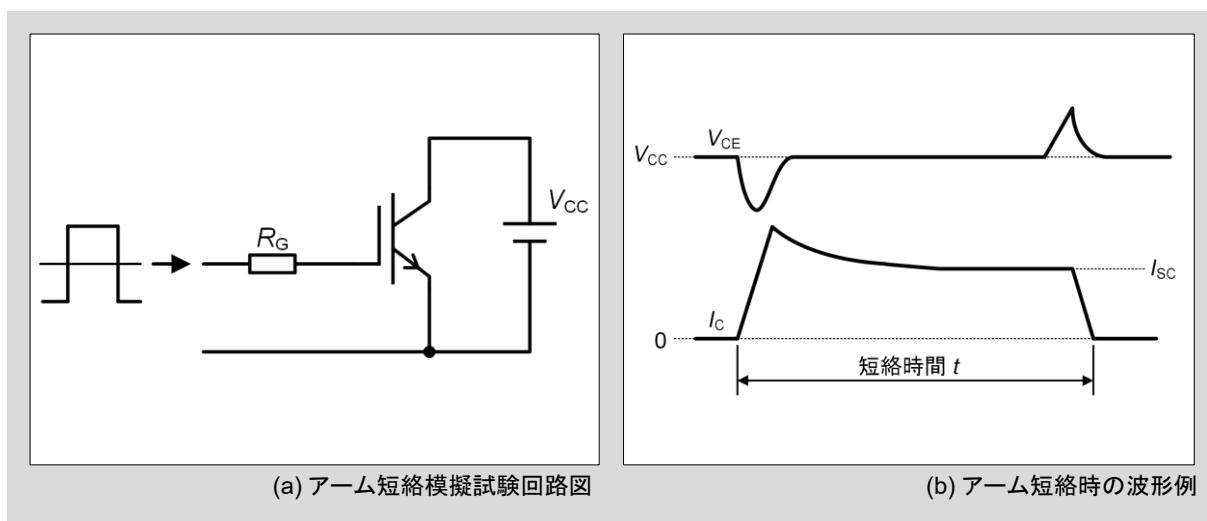

#### 1.1.1 アーム短絡

図5-1にアーム短絡模擬試験回路図と波形例を示します。アーム短絡では、短絡開始と共に $I_C$ は急激に上昇し、飽和後に若干低下します。短絡(飽和)電流値 $I_{SC}$ はG-E間電圧 $V_{GE}$ と素子出力特性および接合温度 $T_{vj}$ で決まり、電源電圧 $V_{CC}$ 、ゲート抵抗 $R_G$ 、パルス幅には殆ど依存しません。

図5-1 アーム短絡模擬試験回路および波形

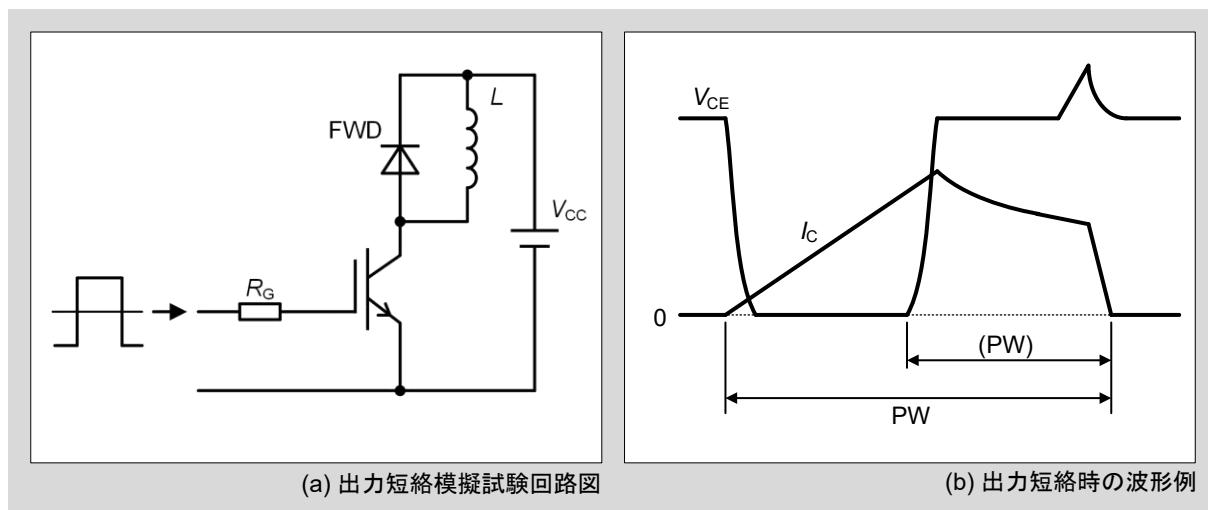

### 1.1.2 出力短絡

図5-2に出力短絡模擬試験回路と波形を示します。出力短絡では短絡線がインダクタンス分を持っているので、短絡開始時の電流波形はアーム短絡の場合と異なります。この場合電流上昇率 $di/dt$ は、

$$di/dt = V_{CC}/L \text{ [A/sec]}$$

で表され、短絡時間を $t$  (sec)とすれば、

$$I_C = di/dt \cdot t \text{ [A]}$$

で計算できます。 $I_C$ 到達値はインダクタンス分や駆動回路( $V_{GE}$ 過渡上昇)などに依存しますが、ピーク値に達し、飽和した後は $V_{CE}$ が上昇しアーム短絡時と同じになります。

電流上昇中、 $V_{CC}$ はインダクタンス $L$ にかかり、IGBTにはC-E間飽和電圧 $V_{CE(sat)}$ 程度の電圧が加わります。このとき、IGBTの負荷はアーム短絡と比べてきわめて低いので、この期間は短絡時間内に含めず考えることができます。

図5-2 出力短絡模擬試験回路および波形

## 1.2 短絡モードと発生原因

三相インバーター装置を例として、短絡モードと発生原因について表5-1に示します。

表5-1 短絡モードと発生原因

| 短絡経路    | 原因                        |

|---------|---------------------------|

| アーム短絡   | IGBTまたはダイオードの破壊           |

| 直列アーム短絡 | 制御回路、駆動回路の故障、またはノイズによる誤動作 |

| 出力短絡    | 配線作業など的人為的なミスおよび負荷の絶縁の破壊  |

| 地絡      | 配線作業など的人為的なミスおよび負荷の絶縁の破壊  |

### 1.3 短絡検出方法

以下に短絡検出方法を説明します。ただし、これら検出方法はVシリーズのみ適用可能です。短絡が想定される回路ではXSシリーズを使用しないでください。

#### 1.3.1 過電流検出器による検出

前述したようにIGBTは短時間での保護が必要となるので、過電流検出からターンオフ完了までの各回路の動作遅れ時間が最小になるように設計してください。

なお、IGBTのターンオフ時間は極めて早いので通常のゲート駆動信号で短絡時の過電流を遮断すると $V_{CE}$ の跳ね上がりが大きくなり、IGBTが過電圧で破壊(RBSOA破壊)する可能性があります。過電流を遮断する際は、IGBTのターンオフをゆるやかにさせること(ソフトターンオフ)を推奨します。

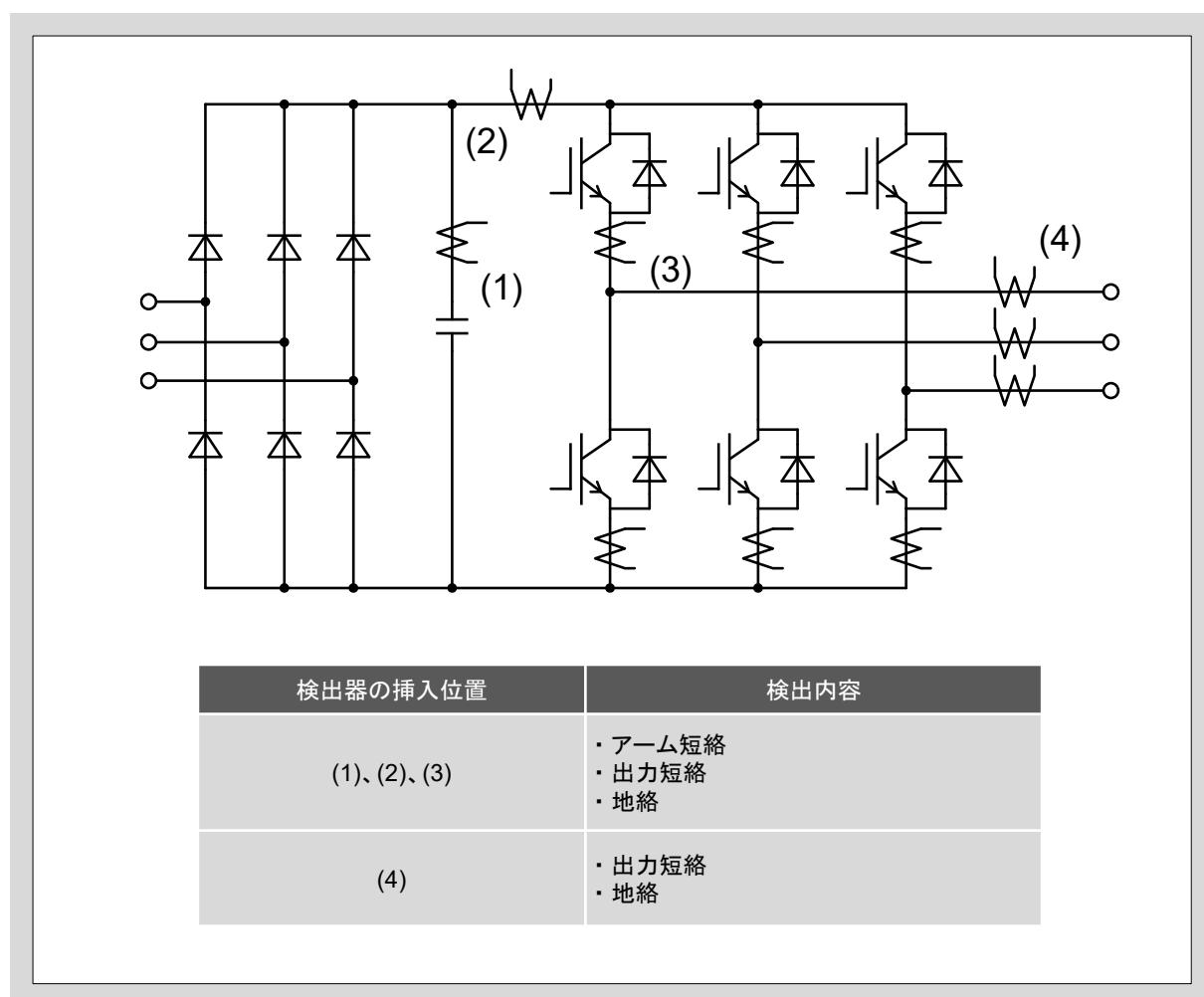

図5-3に過電流検出器の挿入方法を、表5-2にそれぞれの方法の特性と検出可能な内容を示します。どのような保護が必要か検討し、適切な方法を選択してください。

図5-3 過電流検出器の挿入方法

表5-2 過電流検出器の挿入位置と検出内容

| 検出器の挿入位置                  | 特性                                | 検出内容                               |

|---------------------------|-----------------------------------|------------------------------------|

| 平滑コンデンサと直列に挿入<br>図5-3/(1) | ・AC用電流センサ(CT)が使用可能<br>・検出精度が低い    | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| インバータの入力に挿入<br>図5-3/(2)   | ・DC用CTの使用が必要<br>・検出精度が低い          | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| 各素子と直列に挿入<br>図5-3/(3)     | ・DC用CTの使用が必要<br>・検出精度が高い          | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| インバータの出力に挿入<br>図5-3/(4)   | ・高周波出力の装置ではAC用CTの使用可能<br>・検出精度が高い | ・出力短絡<br>・地絡                       |

### 1.3.2 $V_{CE(sat)}$ による検出

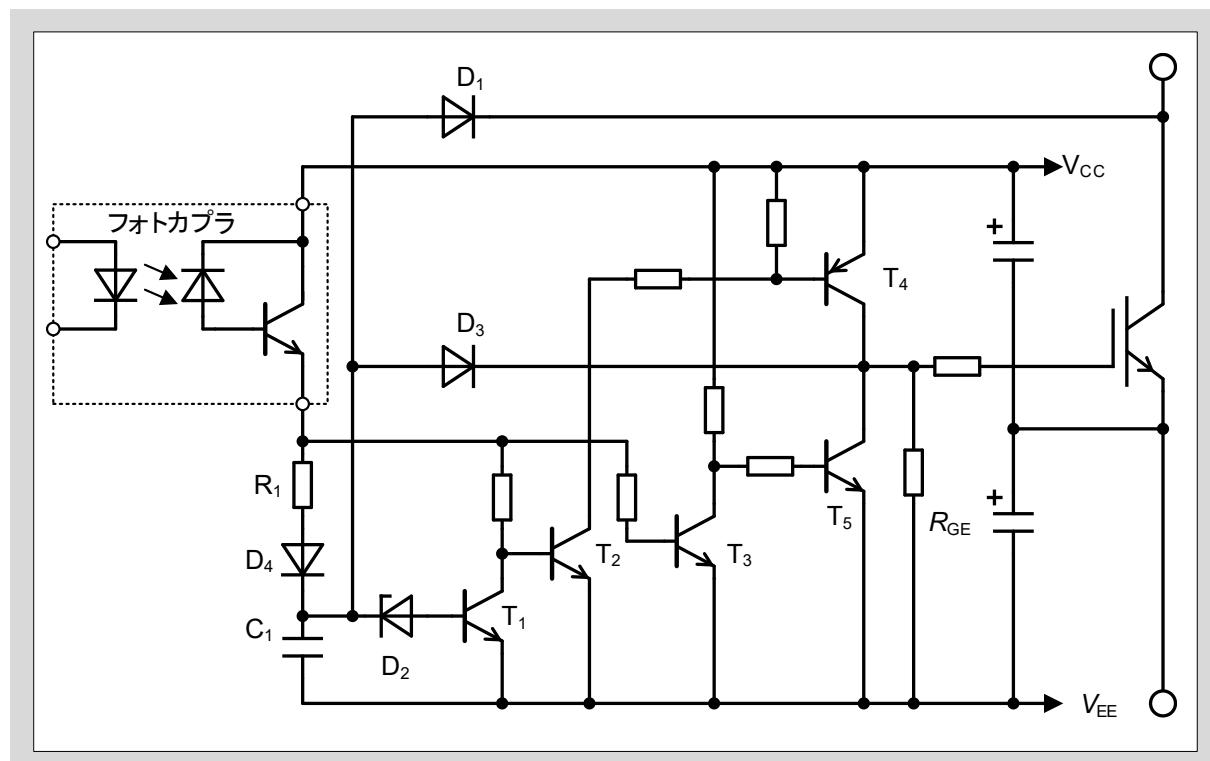

この方法は、表5-1に示す全ての短絡事故に対する保護が可能であり、過電流検出から保護までの動作がゲート駆動回路側で行われるので、最も高速な保護動作が可能となります。図5-4に  $V_{CE(sat)}$  検出による短絡保護回路例を示します。

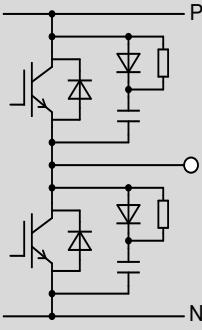

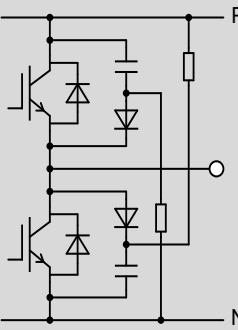

図5-4  $V_{CE(sat)}$ 検出による短絡保護回路例

この回路はIGBTのC-E間電圧をダイオードD<sub>1</sub>を介して監視する回路です。

ターンオン：フォトカプラがオンするとトランジスタT<sub>2</sub>、T<sub>4</sub>がオンしIGBTに+のゲート電圧を印加します。またフォトカプラのオンにより、抵抗R<sub>1</sub>とダイオードD<sub>4</sub>を通してコンデンサC<sub>1</sub>を充電します。このときC<sub>1</sub>の電圧によって、動作が変わります。

【短絡保護動作】

IGBTオン後、短絡状態が発生するとIGBTのV<sub>CE</sub>が上昇します。IGBTのV<sub>CE</sub>が[C<sub>1</sub>の電圧-D<sub>1</sub>の電圧(V<sub>F</sub>-V<sub>EE</sub>)]より高くなると、D<sub>1</sub>がオフとなり、C<sub>1</sub>の電圧が再び上昇します。

C<sub>1</sub>の電圧が[ツエナーダイオードD<sub>2</sub>のV<sub>Z</sub>+トランジスタT<sub>1</sub>のV<sub>BE</sub>]より高くなると短絡保護動作します。

短絡保護動作では、D<sub>2</sub>を通してT<sub>1</sub>のベースに電流が流れT<sub>1</sub>がオンします。T<sub>1</sub>オンによりT<sub>2</sub>、T<sub>4</sub>がオフし、印加していた+のゲート電圧が遮断されます。

フォトカプラはオンしているため、トランジスタT<sub>3</sub>オン、トランジスタT<sub>5</sub>オフ状態を保持しています。T<sub>4</sub>、T<sub>5</sub>が同時オフとなるためゲート蓄積電荷はR<sub>GE</sub>を通してゆっくり放電します。この効果によりIGBTがターンオフする際の過大なサージ電圧の発生を抑制できます。

【通常動作】

IGBTオン後、C<sub>1</sub>の電圧が[D<sub>2</sub>のV<sub>Z</sub>+T<sub>1</sub>のV<sub>BE</sub>]以下の電圧を保持することで、IGBTのオン状態を保持します。

フォトカプラがオフするとT<sub>2</sub>、T<sub>4</sub>オフ、T<sub>3</sub>オフ、T<sub>5</sub>オンとなり、IGBTに-のゲート電圧を印加します。C<sub>1</sub>の電荷はダイオードD<sub>3</sub>、T<sub>5</sub>を通して放電し0Vにリセットします。

上記動作シーケンスからわかるように、短絡保護は各パルスごとで動作します。

## 2. 過電圧保護

### 2.1 過電圧の発生要因と抑制方法

#### 2.1.1 過電圧発生要因

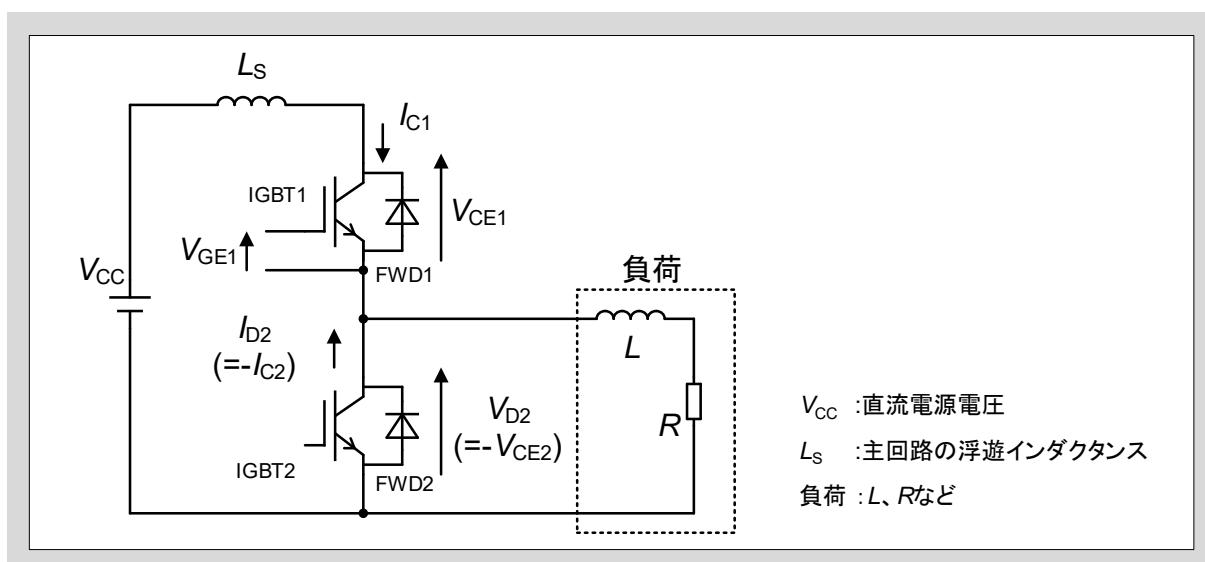

IGBTはスイッチング速度が速いため、IGBTターンオフ時、またはFWD逆回復時に高い $dV/dt$ を発生し、ディスクリートIGBT周辺の配線インダクタンス $L_s$ によるターンオフサージ電圧 $V_{CEP} = L_s \cdot (di/dt)$ が発生します。

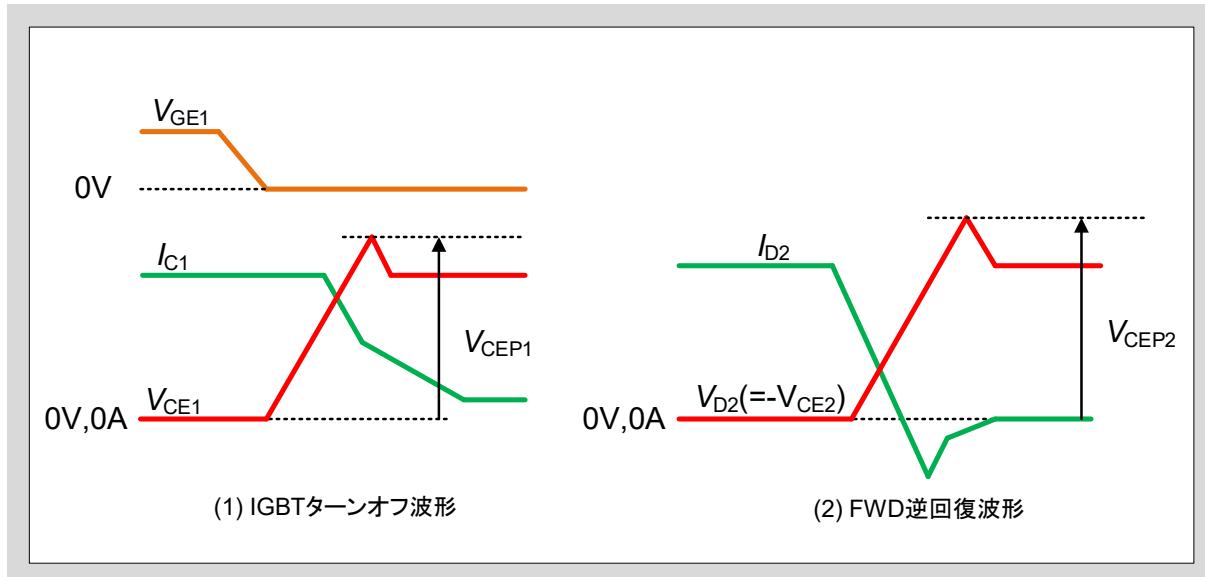

ここではIGBTターンオフ時の電圧・電流波形を例にとって発生要因と抑制方法を紹介し、具体的な回路例(IGBT、FWD共に適用可)を説明します。ターンオフサージ電圧を測定するための簡易的な回路として図5-5に回路例を、図5-6にIGBTのターンオフ波形とFWDの逆回復波形を示します。

図5-5 チョッパ回路

図5-6 動作波形

ターンオフサージ電圧はIGBTがターンオフする際の主回路電流の急激な変化によって、主回路の浮遊 $L_S$ に高い電圧が誘起されることにより発生します。

ターンオフサージ電圧の尖頭値は次式で求められます。

$$V_{CESP} = V_{CC} + \left(-L_S \cdot \frac{dI_C}{dt}\right) \quad dI_C/dt: \text{ターンオフ時のコレクタ電流変化率の最大値}$$

$V_{CESP}$ がIGBTのC-E間耐圧 $V_{CES}$ を超えると破壊に至ることがあります。

### 2.1.2 過電圧抑制方法

過電圧発生要因であるターンオフサージ電圧を抑制する方法として下記の方法があります。

- IGBTにスナバなどの保護回路を付けてサージ電圧を抑制する。スナバ回路のコンデンサにはフィルムコンデンサを用い、ディスクリートIGBTの近くに配置して高周波サージ電圧を抑制させる。

- IGBT駆動回路の $-V_{GE}$ や $R_G$ を調整し $dI/dt$ を小さくする(詳細は第7章を参照してください)。

- 電解コンデンサをできるだけIGBTの近くに配置し、 $L_S$ を低減する。低インピーダンスタイプのコンデンサを用いるとさらに効果的。

- 主回路およびスナバ回路の $L_S$ を低減するために、配線をより太く・短くする。

- ゲート駆動回路にアクティブクランプ回路を適用し、配置したツェナーダイオードの降伏電圧と概ね等しいサージ電圧に抑制する。

## 2.2 スナバ回路の種類と特徴

スナバ回路には全ての素子に1対1で付ける個別スナバ回路と直流母線間に一括で付ける一括スナバ回路があります。

### 2.2.1 個別スナバ回路

個別スナバ回路の代表的な例として、下記のスナバ回路があります。

- RCスナバ回路

- 充放電形RCDスナバ回路

- 放電阻止形RCDスナバ回路

表5-3に各個別スナバ回路の接続図と特性および主な用途を示します。

### 2.2.2 一括スナバ回路

一括スナバ回路の代表的な例として、下記のスナバ回路があります。

- Cスナバ回路

- RCDスナバ回路

最近ではスナバ回路簡素化の目的で一括スナバ回路が使用されることが多くなってきています。

表5-4に各一括スナバ回路の接続図と特性および主な用途を示します。

**表5-3 個別スナバ回路の接続図**

| スナバ回路接続図                                                                                                    | 特 性(注意事項)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RCスナバ回路</b><br>         | <ul style="list-style-type: none"> <li>一括スナバ回路に比べサージ電圧抑制効果が大きい。</li> <li>大容量のIGBTに適用する際には、スナバ抵抗を低い値にする必要があり、この結果ターンオン時の<math>I_C</math>が増大しIGBTの負担が大きくなる。</li> </ul>                                                                                                                                                                                                                                                                                                 |

| <b>充放電形RCDスナバ回路</b><br>   | <ul style="list-style-type: none"> <li>サージ電圧抑制効果あり。</li> <li>RCスナバ回路と異なり、スナバダイオードが追加されているのでスナバ抵抗値を大きくでき、ターンオン時のIGBTの負担を考えなくてよい。</li> <li>充放電形RCDスナバ回路のスナバ抵抗における発生損失は下式で求められる。</li> </ul> $P = \frac{L_S \cdot I_0^2 \cdot f}{2} + \frac{C_S \cdot V_{CC}^2 \cdot f}{2}$ <p> <math>L_S</math> : 主回路の浮遊インダクタンス<br/> <math>I_0</math> : IGBTのターンオフ時コレクタ電流<br/> <math>C_S</math> : スナバコンデンサ容量<br/> <math>V_{CC}</math> : 直流電源電圧<br/> <math>f</math> : スイッチング周波数     </p> |

| <b>放電阻止形RCDスナバ回路</b><br> | <ul style="list-style-type: none"> <li>サージ電圧抑制効果あり。</li> <li>スナバ回路での発生損失が少ない。</li> <li>放電阻止形RCDスナバ回路のスナバ抵抗における発生損失は下式で求められる。</li> </ul> $P = \frac{L_S \cdot I_0^2 \cdot f}{2}$ <p> <math>L_S</math> : 主回路の浮遊インダクタンス<br/> <math>I_0</math> : IGBTのターンオフ時コレクタ電流<br/> <math>f</math> : スイッチング周波数     </p>                                                                                                                                                              |

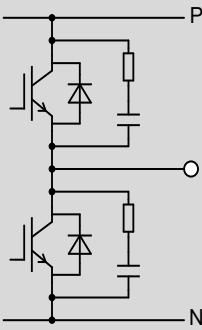

**表5-4 一括スナバ回路の接続図**

| スナバ回路接続図                                                                                              | 特 性(注意事項)                                                                                                      |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| <b>Cスナバ回路</b><br>    | <ul style="list-style-type: none"> <li>最も簡易的な回路</li> <li>主回路インダクタンスとスナバコンデンサとによるLC共振回路により電圧が振動し易い。</li> </ul>  |

| <b>RCDスナバ回路</b><br> | <ul style="list-style-type: none"> <li>スナバダイオードの選定を誤ると高いサージ電圧が発生することや、スナバダイオードの逆回復時に電圧が振動することがあります。</li> </ul> |

## 2.3 放電阻止形RCDスナバ回路の設計方法

IGBTのスナバ回路として、最も合理的と思われる放電阻止形RCDスナバ回路の基本的な設計方法について説明します。

### 2.3.1 適用可否の検討

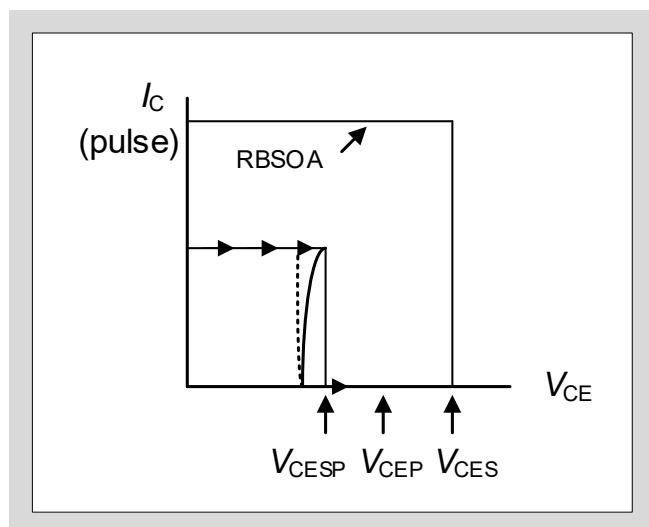

図5-7に放電阻止形RCDスナバ回路を適用した場合のターンオフ時の動作軌跡を示します。

図5-7 ターンオフ時の動作軌跡

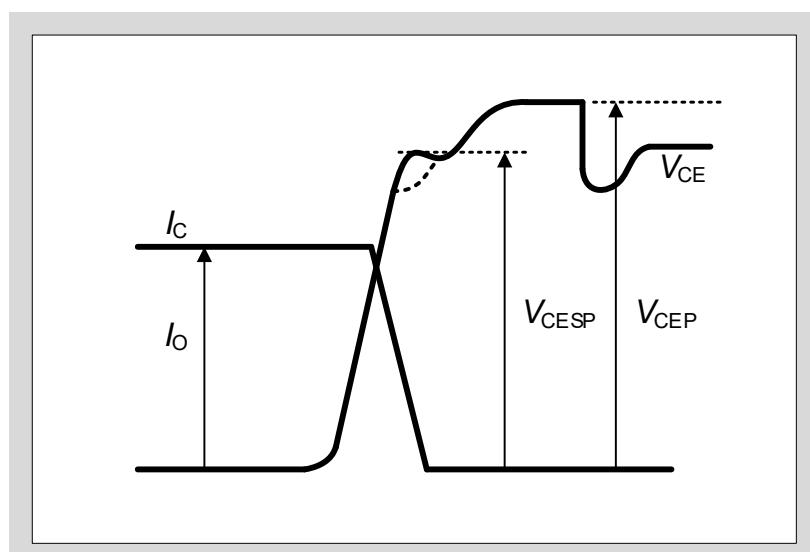

図5-8にターンオフ時の電流・電圧波形を示します。放電阻止形RCDスナバはIGBTの  $V_{CE}$  が直流電源電圧を超えてから動作し、その理想的な動作軌跡は点線で示されています。

しかし実際の装置ではスナバ回路の配線インダクタンスやスナバダイオード過渡順電圧降下の影響によるターンオフ時のサージ電圧が存在するため、実線のように膨らみます。

図5-8 ターンオフ時の電流・電圧波形

放電阻止形RCDスナバ回路を適用するためには、適用後のターンオフ動作軌跡がIGBTのRB SOA内に収まっているか検証する必要があります。

なお、ターンオフ時のサージ電圧は次式で求められます。

$$V_{CESP} = E_d + V_{FM} + \left( -L_S \cdot \frac{dI_c}{dt} \right)$$

$E_d$  : 直流電源電圧

$V_{FM}$  : スナバダイオード過渡順電圧降下※

※ スナバダイオードの一般的な過渡順電圧降下の参考値は下記の通りです。

600Vクラス: 20~30V

1200Vクラス: 40~60V

$L_S$  : スナバ回路の配線インダクタンス

$dI_c/dt$  : ターンオフ時のコレクタ電流変化率最大値

### 2.3.2 スナバコンデンサ( $C_s$ )容量値の求め方

スナバコンデンサに必要な容量値は次式で求められます。

$$C_s = \frac{L_s \cdot I_0^2}{(V_{CEP} - E_d)^2}$$

$L_s$  : 主回路の配線インダクタンス

$I_0$  : IGBTのターンオフ時コレクタ電流

$V_{CEP}$  : スナバコンデンサ電圧の最終到達値

$E_d$  : 直流電源電圧

$V_{CEP}$ はIGBTの $V_{CES}$ 以下に抑える必要があります。また、スナバコンデンサには高周波特性の良いもの(フィルムコンデンサなど)を選んでください。

### 2.3.3 スナバ抵抗( $R_s$ )値の求め方

スナバ抵抗への要求機能は、IGBTが次のターンオフ動作を行うまでにスナバコンデンサの蓄積電荷を放電する事です。IGBTが次のターンオフ動作を行うまでに、蓄積電荷の90%を放電する条件でスナバ抵抗を求める式次式のようになります。

$$R_s \leq \frac{1}{2.3 \cdot C_s \cdot f}$$

$R_s$  : スナバ抵抗

$C_s$  : スナバコンデンサ容量

$f$  : スイッチング周波数

スナバ抵抗値をあまりにも低い値に設定すると、スナバ回路電流が振動しIGBTのターンオン時のコレクタ電流尖頭値も増えるので、式を満足する範囲内で極力高い値に設定してください。

スナバ抵抗の発生損失 $P(R_s)$ は抵抗値と関係なく次式で求められます。

$$P(R_s) = \frac{L_s \cdot I_0^2 \cdot f}{2}$$

$P(R_s)$  : スナバ抵抗の発生損失

$L_s$  : 主回路の配線インダクタンス

$I_0$  : IGBTのターンオフ時コレクタ電流

$f$  : スイッチング周波数

#### 2.3.4 スナバダイオードの選定

スナバダイオードの過渡順電圧降下は、ターンオフ時のサージ電圧発生要因の一つになります。またスナバダイオードの逆回復時間が長いと、高周波スイッチング動作時にスナバダイオードの発生損失が大きくなり、スナバダイオードの逆回復が急激であると、スナバダイオードの逆回復動作時にIGBTのC-E間電圧が急激に大きく振動します。スナバダイオードには、過渡順電圧が低く、逆回復時間が短く、逆回復動作がソフトなものを選んでください。

#### 2.3.5 スナバ回路配線上の注意事項

スナバ回路の $L_S$ はサージ電圧発生要因となりますので、回路部品の配置も含めてインダクタンス低減の工夫を行ってください。

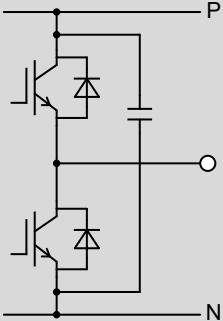

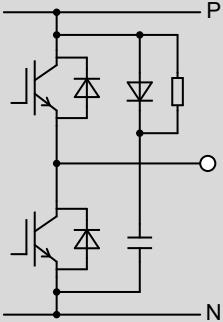

## 2.4 サージ電圧抑制回路 ークランプ回路構成例ー

一般的に、主回路インダクタンスの低減やスナバ回路を設けることによってC-E間のサージ電圧を抑制することができます。しかしながら装置の運転条件などによってはサージ電圧の抑制が困難な場合があります。このような場合に用いられるサージ電圧抑制回路の1つとしてアクティブクランプ回路があります。

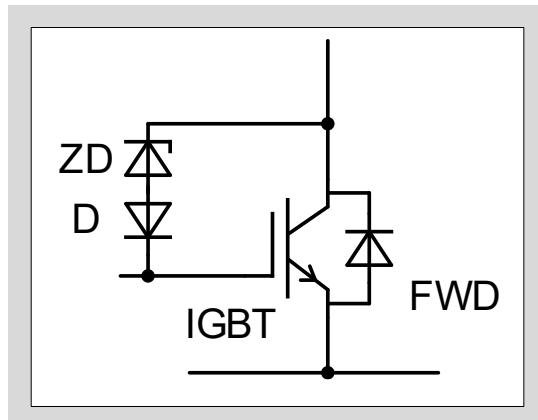

図5-9にアクティブクランプ回路の一例を示します。基本的な回路構成は、C-G間にツエナーダイオードを付加するとともに、そのツエナーダイオードと逆通電方向にダイオードを直列に接続しています。

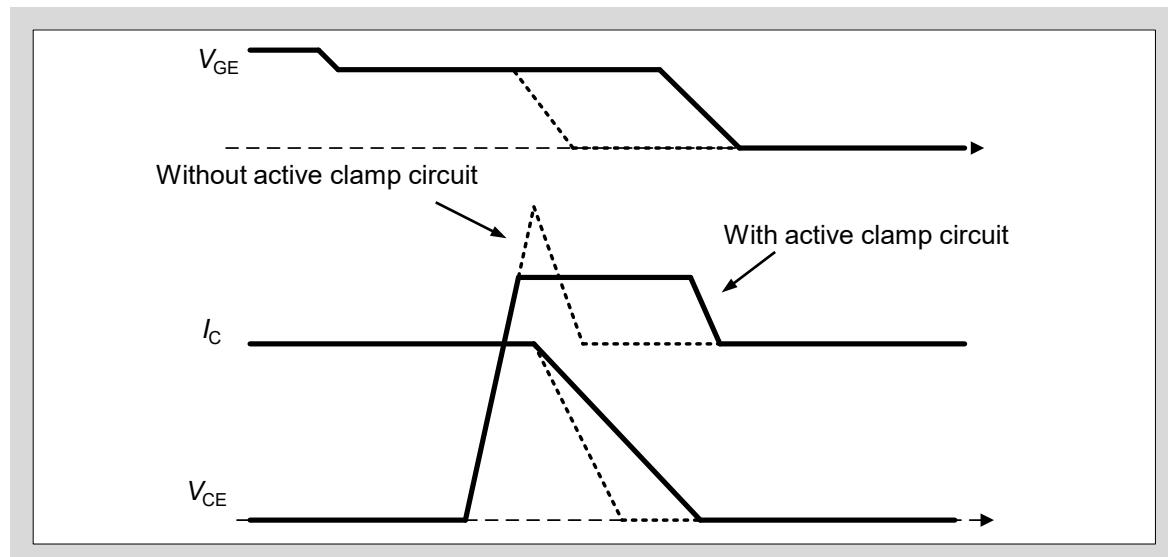

この回路でC-E間にツエナーダイオードの降伏電圧を超える電圧が発生した場合、ツエナーダイオードが降伏しコレクタからゲートに電流が流れます。この電流と $R_G$ によりG-E間に+電圧が加わります。+電圧がIGBTのG-E間しきい値電圧 $V_{GE(th)}$ を超えるとIGBTに $I_C$ が流れ、 $V_{CE}$ はツエナーダイオードの降伏電圧と概ね等しくなるようにクランプします。アクティブクランプ回路を設けることでサージ電圧抑制が可能となります。

一方、ツエナーダイオードの降伏電流はIGBTをオンさせるように流れるため、ターンオフ時の電流変化率 $di/dt$ はクランプ回路付加前より緩やかになり、ターンオフ時間が長くなり(図5-10参照)、ターンオフ損失が増えますので、各種設計検証を行った上でクランプ回路を適用してください。

図5-9 アクティブクランプ回路例

図5-10 アクティブクランプ回路適用時の波形例