## ディスクリートIGBT

### Application Manual

注意

1. この資料の内容(製品の仕様、特性、データ、材料、構造など)は2025年12月現在のものです。この内容は製品の仕様変更のため、または他の理由により事前の予告なく変更されることがあります。この資料に記載されている製品を使用する場合には、その製品の最新版の仕様書を入手して、データを確認してください。

2. 本資料に記載してある応用例は富士電機製品を使用した代表的な応用例を説明するものであり、本資料によって工業所有権、その他権利の実施に対する保証または実施権の許諾を行うものではありません。

3. 富士電機は絶えず製品の品質と信頼性の向上に努めています。しかし、半導体製品は故障が発生したり、誤動作する場合があります。富士電機製半導体製品の故障または誤動作が、結果として人身事故、火災等による財産に対する損害や、社会的な損害を起こさないように冗長設計、延焼防止設計、誤動作防止設計などの安全確保をお客様の責任において行ってください。

4. 本資料に記載している製品は、普通の信頼度が要求される下記のような電子機器や電気機器に使用されることを意図して造られています。

- ・コンピュータ・OA機器・通信機器(端末)・計測機器・工作機械

- ・オーディオビジュアル機器・家庭用電気製品・パーソナル機器・産業用ロボットなど

5. 本仕様書に記載されている製品は、人命に関わるような状況下で使用される機器あるいはシステムに用いられる事を目的として設計・製造されたものではありません。以下に示す機器あるいはシステムへの適用に関し、富士電機は一切の責任を負いません。

- ・幹線用通信機器・交通信号機・医療機器

- ・ガス警報器および遮断機・防災/防犯装置・安全確保のための各種装置

6. 極めて高い信頼度を要求される下記のような機器および戦略物資に該当する機器には、本仕様書に記載の製品を使用しないでください。

- ・車両機器(自動車、鉄道、船舶など)・宇宙機器・航空機搭載用機器

- ・原子力制御機器・海底中継機器

7. 本資料の一部または全部の転載複製については、文書による弊社の承諾が必要です。

8. 本資料の内容にご不明の点がありましたら、製品を使用する前に富士電機(株)または、その販売店へ質問してください。本注意書きの指示に従わないために生じたいかなる損害も富士電機(株)とその販売店は責任を負うものではありません。

## 第8章 ディスクリートIGBTの並列接続

|                   |      |

|-------------------|------|

| 1. ディスクリートIGBTの選定 | 8-2  |

| 2. 主回路の設計         | 8-6  |

| 3. ゲート駆動回路の設計     | 8-8  |

| 4. 放熱設計           | 8-11 |

大電流を制御する回路に適用する際、ディスクリートIGBTを並列接続して使用すると通電電流能力を増大させることができます。しかし、この場合ディスクリートIGBT間の電流アンバランスや温度分布、配線長の増加によるノイズやサージ電圧の増大等を考慮する必要があります。

上記のような問題を防ぐため、並列接続時に留意すべき点は主に以下の4つです。

1. ディスクリートIGBTの選定

2. 主回路の設計

3. ゲートドライブ回路

4. 熱設計

本章では並列接続する際の各留意点の詳細について記載します。

## 1. ディスクリートIGBTの選定

並列接続する際の留意する点として、同一アーム上の各ディスクリートIGBTにおける $V_{CE(sat)}$ のバラツキ( $\Delta V_{CE(sat)}$ )や温度依存性の特性差が挙げられます。この $\Delta V_{CE(sat)}$ 、すなわち各ディスクリートIGBTの出力特性に差が生じることにより、導通時の定常状態において電流アンバランスが発生します。電流アンバランスが過大になると、電流分担の大きいIGBTの発生損失が増大し、熱破壊する可能性があります。したがって並列接続させるディスクリートIGBTを選定する際は $\Delta V_{CE(sat)}$ を留意する必要があります。この考え方は、FWDにおいても同様になります。

### 1.1 $\Delta V_{CE(sat)}$ による電流アンバランスの考え方

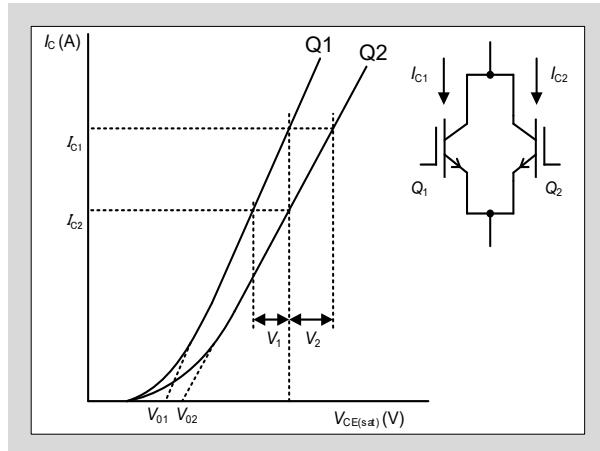

図8-1に異なる $V_{CE(sat)}$ を持つIGBT(Q<sub>1</sub>とQ<sub>2</sub>)の出力特性を示します。Q<sub>1</sub>とQ<sub>2</sub>の $V_{CE(sat)}$ の差を $\Delta V_{CE(sat)}$ とします。図8-1では2並列を例として図示しており、Q<sub>1</sub>とQ<sub>2</sub>の出力特性は以下の式で近似できます。

$$\begin{aligned}V_{CEQ1} &= V_{01} + r_1 \cdot I_{C1} \\r_1 &= V_1 / (I_{C1} - I_{C2}) \\V_{CEQ2} &= V_{02} + r_2 \cdot I_{C2} \\r_2 &= V_2 / (I_{C1} - I_{C2})\end{aligned}$$

したがってQ<sub>1</sub>とQ<sub>2</sub>を並列接続した回路に $I_{Ctotal}(=I_{C1}+I_{C2})$ のコレクタ電流を流した場合、キルヒホッフの法則からQ<sub>1</sub>とQ<sub>2</sub>の電圧が同一になるので、それぞれに流れるIGBTのコレクタ電流は以下のように求めることができます。

$$\begin{aligned}I_{C1} &= (V_{02} - V_{01} + r_2 \cdot I_{Ctotal}) / (r_1 + r_2) \\I_{C2} &= (V_{01} - V_{02} + r_1 \cdot I_{Ctotal}) / (r_1 + r_2)\end{aligned}$$

図8-1 異なる出力特性の組み合わせ例

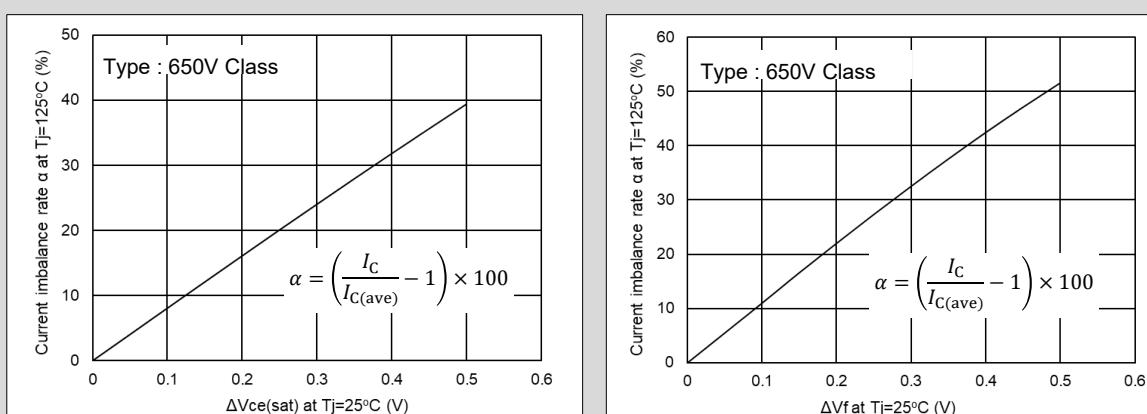

図8-2  $\Delta V$ と電流アンバランス率(左:IGBT、右:FWD)

前述式において  $V_{01}=V_{02}$ とした場合、Q<sub>1</sub>にはQ<sub>2</sub>の電流の  $r_2/r_1$ 倍の電流が流れることになります。図8-1からわかるように  $r_2 > r_1$  であるため、Q<sub>1</sub>の電流分担が大きくなります。このように  $\Delta V_{CE(sat)}$  がある場合には  $V_{CE(sat)}$  が低い方のIGBTの電流分担が大きくなります。

この並列接続時に生じる電流分担の割合は電流アンバランス率と呼ばれ、各IGBTの  $\Delta V_{CE(sat)}$  によって決定されます。図8-2に、2並列接続させたXSシリーズディスクリートIGBTの  $\Delta V_{CE(sat)}$  と電流アンバランス率の関係を示します。 $\Delta V_{CE(sat)}$  が大きくなると電流アンバランス率が大きくなることが分かります。したがって並列接続をする際には  $\Delta V_{CE(sat)}$  が小さい製品を組み合わせることが重要となります。

## 1.2 $\Delta V_{CE(sat)}$ の最小化

良好な電流分担を得るために $\Delta V_{CE(sat)}$ の小さいIGBTを組み合わせる必要があります。 $\Delta V_{CE(sat)}$ は同一製品ロットのディスクリートIGBTを用いることにより最小にすることができます。これは原料のバラツキや製造・検査工程から生じる影響を最小にできるためです。したがって並列接続を行う場合、同一製品型式の同一製品ロットを使用してください。

## 1.3 出力特性の接合温度 $T_{vj}$ 依存性と電流アンバランス

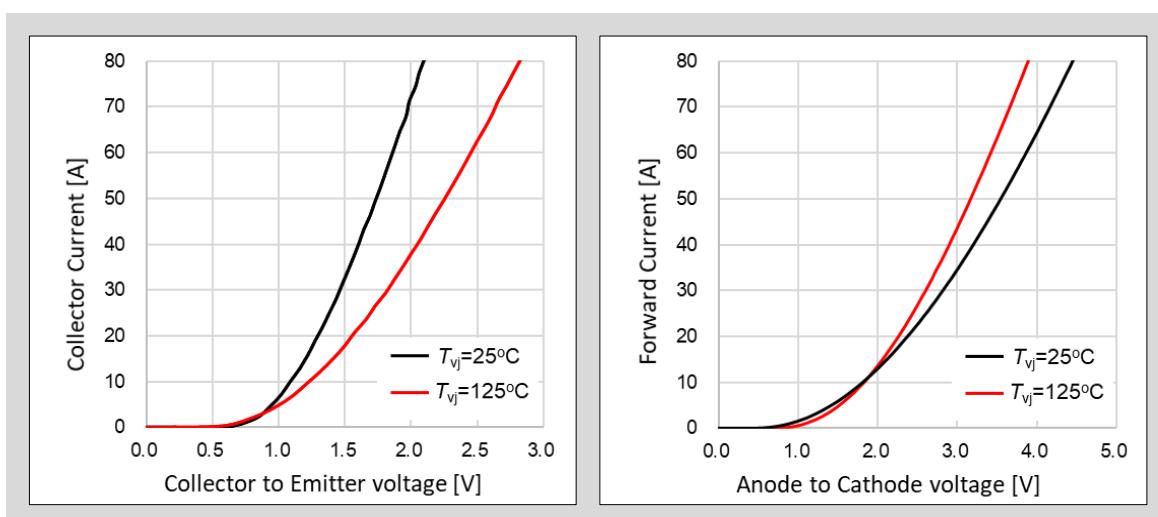

IGBTやFWDの出力特性は接合温度 $T_{vj}$ 依存性を有しており、並列接続されたディスクリートIGBTの電流アンバランスに影響を与えることがあります。並列接続を行う際は留意する必要があります。ここでは40A定格のXSシリーズディスクリートIGBTを例として、図8-3にIGBTとFWDの出力特性を示します。

本章1.1で述べたように、 $\Delta V_{CE(sat)}$ があるIGBTを2並列接続した時、 $V_{CE(sat)}$ の低いIGBTの電流分担が大きくなります。これにより $V_{CE(sat)}$ の低いIGBTの発生損失が大きくなり、 $T_{vj}$ はもう一方よりも上昇します。IGBTは正の温度特性を有するため、 $T_{vj}$ が上昇するにつれて $V_{CE(sat)}$ が高くなるので、それに伴い電流分担は小さくなります。このように、IGBTの並列接続の場合では、温度上昇によって並列接続された双方のIGBTに流れる電流がバランスしあう方向に作用します。

一方で、FWDは負の温度特性を有するため、 $\Delta V_F$ があるFWDを2並列接続した時、 $T_{vj}$ の上昇に伴い $V_F$ が低くなるので、それに伴い電流アンバランスを増長する方向に作用します。

従って、IGBTやFWDを並列接続する場合、 $T_{vj}$ の上昇によって電流アンバランス率に影響を及ぼします。図8-2に記載の電流アンバランス率はこの現象を考慮していますので、FWDのアンバランス率の方が大きくなっています。

図8-3 出力特性比較(左:IGBT、右:FWD)

## 1.4 多並列接続時のディレーティング

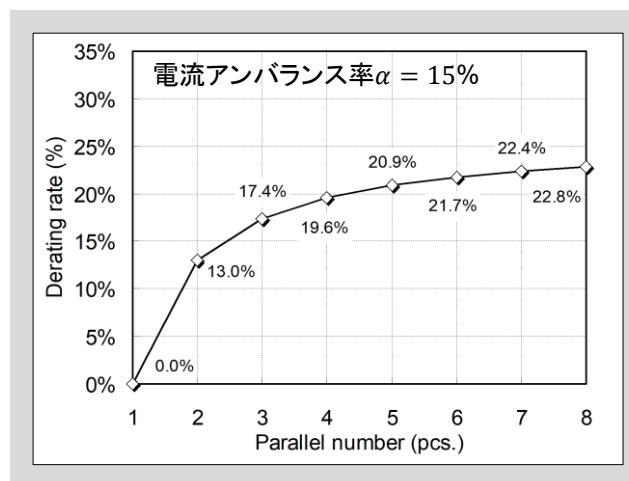

IGBTの並列接続時には電流アンバランスを考慮する必要があり、その電流総和(流すことができる最大電流)は定格電流の総和に対するディレーティング(電流低減)が必要となります。n個の素子を並列接続する場合、最も $V_{CE(sat)}$ が低い1素子への電流集中が最悪条件と考えます。n個の素子を並列接続した場合の許容最大電流 $\Sigma I$ は、2並列時の電流アンバランス率 $\alpha$ を用いて以下の式で表すことができます。

$$\sum I = I_{C(\max)} \left[ 1 + (n - 1) \frac{\left(1 - \frac{\alpha}{100}\right)}{\left(1 + \frac{\alpha}{100}\right)} \right] \quad \alpha = \left( \frac{I_{C1}}{I_{C(\text{ave})}} - 1 \right) \cdot 100$$

ここで上式の電流アンバランス率 $\alpha$ は図8-1に示した2並列時の電流値 $I_{C1}$ と平均電流値 $I_{C(\text{ave})}=(I_{C1}+I_{C2})/2$ により求められます。また $I_{C(\max)}$ は1素子当りの最大電流、 $\Sigma I$ は並列接続時の最大電流を表しています。この $\Sigma I$ を流すためには並列接続した全ての素子が仕様書に記載のRBSOAを満足する必要があるとともに、発生損失によって生じる接合温度の上昇を $T_{vj(max)}$ 以下にする必要があります。特に発生損失による接合温度の上昇は使用条件(スイッチング周波数、ゲート駆動条件、放熱条件、スナバ条件等)により異なるので注意が必要です。

たとえば $\alpha=15\%$ 、 $I_{C(\max)}=40A$ 、 $n=4$ の場合では $\Sigma I \approx 128.7$ となり単純に $40 \times 4 = 160A$ とはならず約19.6%のディレーティングが必要であることがわかります。このように並列時の全電流 $\Sigma I$ は、単純な電流総和( $n \times I_{C(\max)}$ )に対してディレーティングが必要となります。

電流アンバランス率 $\alpha=15\%$ とした場合のIGBTのディレーティング率を図8-4に示します。この図からわかるように、並列数の増加とともにディレーティング率が大きくなっています。したがって並列接続を行う際、接続数に応じたディレーティングを行ってください。またディレーティング率は電流アンバランス率によって異なりますので、注意してください。

本例に示すディレーティング率は前記の電流アンバランス率から求めた参考値ですので、実機動作によってアンバランス確認と検証を行った上でディレーティング率を決定してください。

図8-4 並列接続数とディレーティング率の関係

## 2. 主回路の設計

並列接続された各ディスクリートIGBT間の主回路配線におけるバラツキは、定常動作とスイッチング動作時の電流アンバランスに大きな影響を与えます。これは誤動作の誘因になる可能性があるため、並列接続の主回路設計を行う際は主に次の2点を留意し、主回路を均等かつ短く設計する必要があります。

- (1) 主回路配線抵抗のバラツキ

- (2) 主回路配線インダクタンスのバラツキ

### 2.1 主回路配線抵抗のバラツキ

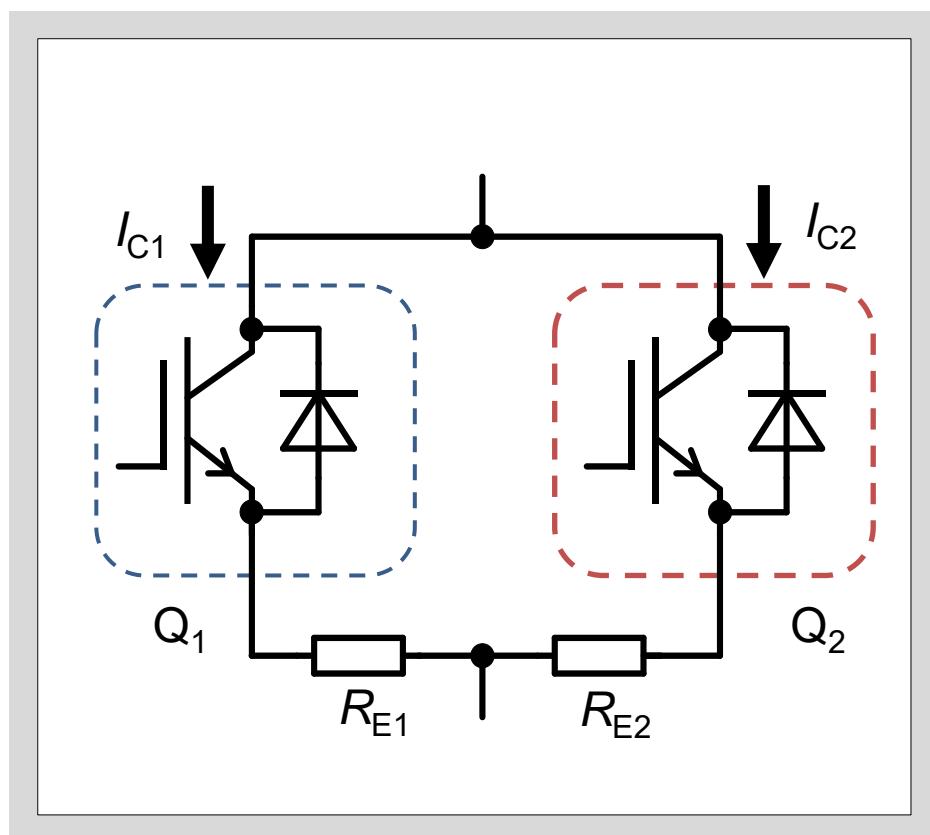

図8-5に主回路配線抵抗を示した2並列接続時の簡易等価回路を示します。ここではコレクタ側の抵抗成分を省略して記載しています。

この主回路配線の抵抗成分が大きい場合、抵抗成分が小さい場合と比べ、オームの法則に従い $Q_1$ と $Q_2$ に流れるコレクタ電流の合計は減少し、この抵抗成分が大きい程、コレクタ電流の合計は小さくなります。

さらに主回路配線の左右で抵抗に不均等があり、 $R_{E1} > R_{E2}$ と仮定した場合、 $I_{C1} < I_{C2}$ となり、 $Q_1$ と $Q_2$ で電流アンバランスが生じます。

このように主回路の抵抗成分によって、コレクタ電流の減少や電流アンバランスが発生する可能性があります。したがってこの影響を低減するためには、エミッタ側の配線は極力短くかつ均等にする必要があります。

図8-5 主回路配線に抵抗成分がある場合の等価回路図

## 2.2 主回路配線インダクタンスのバラツキ

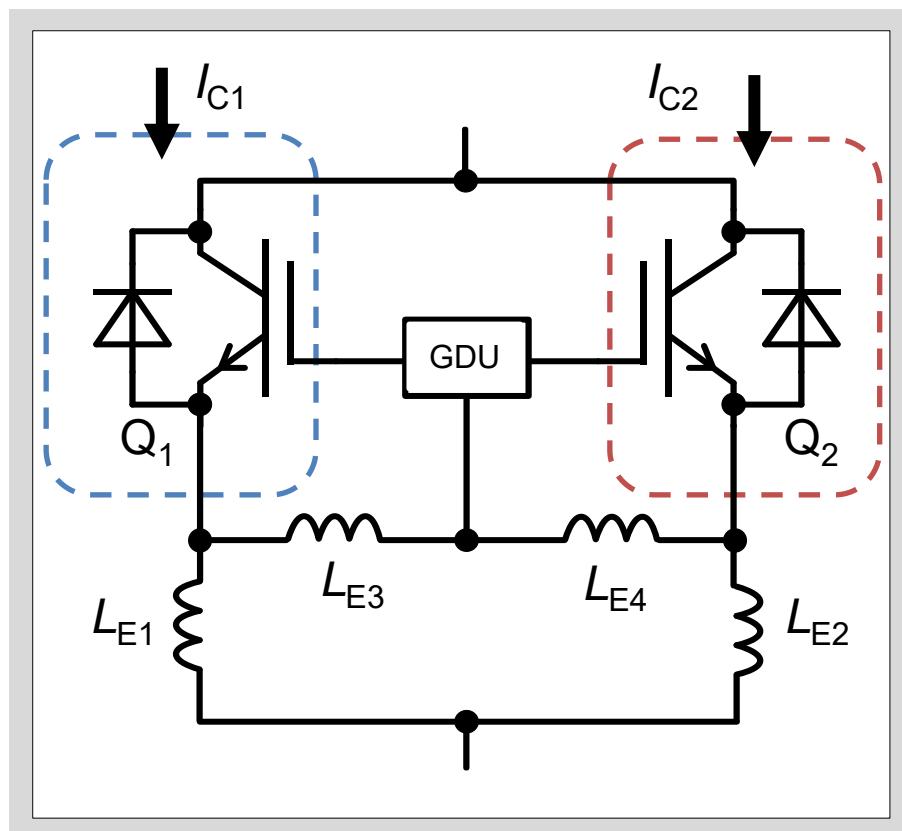

図8-6に主回路配線インダクタンスを示した2並列接続時の簡易等価回路を示します。主回路配線のインダクタンスが左右で不均等の場合、並列接続した各IGBTのスイッチング時の電流分担にアンバランスが生じます。 $Q_1$ と $Q_2$ のIGBTに流れるコレクタ電流をそれぞれ $I_{C1}$ 、 $I_{C2}$ としたとき、電流分担は各IGBTの配線インダクタンス $L_{E1}$ と $L_{E2}$ の差に影響を受け、ほぼインダクタンス比によって決まります。したがってスイッチング時の電流アンバランスを緩和するためには配線インダクタンス長をできる限り均等にすることが必要です。 $L_{E1}$ と $L_{E2}$ の配線インダクタンスが異なる場合、ターンオン時の電流の時間的変化( $di/dt$ )によって発生する $L_{E1}$ と $L_{E2}$ の誘起電圧に差が生じます。誘起電圧の差は並列接続した各IGBTの実効的に印加されるゲート電圧に影響を与え、電流アンバランスを助長します。このことから、並列接続を行う際、主回路配線は可能な限り $L_{E1}=L_{E2}$ となる配線にすることが重要となります。また、主回路配線インダクタンスが大きいとIGBTターンオフ時のサーボ電圧が大きくなるため、配線インダクタンスはできる限り小さくする必要があります。

図8-6 主回路配線インダクタンスを考慮した並列接続時の簡易等価回路

### 3. ゲート駆動回路の設計

ディスクリートIGBTの並列接続におけるゲート駆動回路の設計方法には、第4章の内容に加え並列接続時特有の留意点があります。また、これは並列接続時のゲートドライバ構成によって留意すべき点が異なります。この留意点を考慮しない場合、ゲート駆動回路が原因で電流アンバランスや誤動作が発生し、ディスクリートIGBTが破壊する可能性があります。下記では並列接続におけるゲート駆動回路設計時に留意すべき主な点を説明します。

#### 3.1 ゲート駆動回路とゲート - エミッタ端子の接続方法

並列駆動させる際、ディスクリートIGBTに補助エミッタ端子がある場合は、補助エミッタ端子を用いてゲート駆動してください。補助エミッタ端子がない場合にゲート駆動回路のエミッタ配線を、図8-6に示した配線インダクタンス  $L_{E1}$  と  $L_{E2}$  が不均衡となるような位置に接続すると、スイッチング時の各ディスクリートIGBTのゲート電圧挙動に差異が発生し、過渡的な電流分担がアンバランスになります。TO-247-4パッケージにはゲート駆動回路用に補助エミッタ端子を設けており、この端子を使用すれば、 $L_{E1}$  と  $L_{E2}$  が均等になるので、過渡的な電流アンバランスを抑制することができます。

しかし補助エミッタ端子を用いてゲートを駆動した場合でも、ゲート駆動回路から各ディスクリートIGBTまでのエミッタ配線が長く、不均等になれば電流アンバランスを引き起こします。したがって並列接続した各ディスクリートIGBTへのゲート駆動回路の配線は均等な長さで最短かつ対称となるように設計してください。このとき、ゲート駆動回路の配線は主回路配線からはできるだけ遠ざけ平行にならないようにし、相互誘導(特にコレクタ電流)を受けないように配置してください。

#### 3.2 並列接続時のゲート駆動回路の留意点

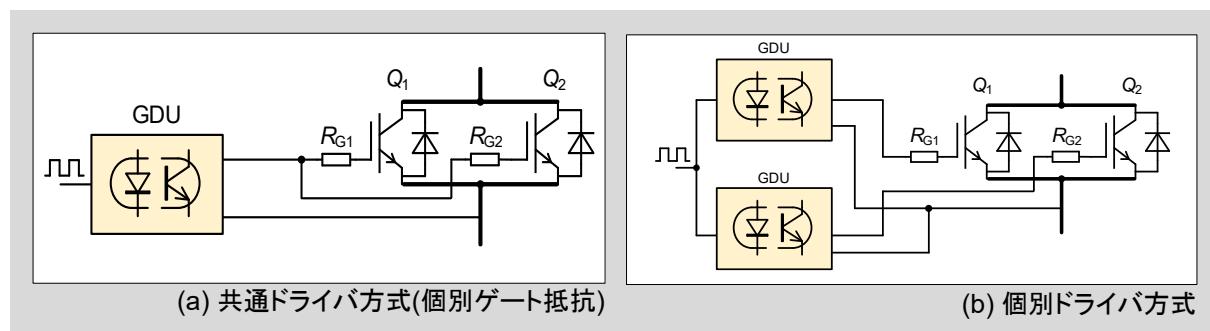

ディスクリートIGBTの並列接続におけるゲート駆動回路の方式は、多岐にわたり、ゲートドライバ構成によって留意すべき点が異なります。並列接続におけるゲート駆動回路の構成例として、図8-7(a)に共通ドライバ方式(1つのゲート駆動回路で並列接続された各ディスクリートIGBTを動作させる構成)を示し、図8-7(b)に個別ドライバ方式(並列数分のゲート駆動回路で各ディスクリートIGBTを動作させる構成)を示します。以降のページでは、この代表的な2つのゲート駆動回路の方式の詳細とその設計時の留意点について説明します。

図8-7 並列接続時のドライバ構成

### 3.2.1 並列駆動における共通ドライバ方式について

共通ドライバ方式の特性として、並列接続されたディスクリートIGBTを駆動させる電源やフォトカプラを共通に出来るため、ゲート駆動回路を簡素化でき部品点数を少なくすることが挙げられます。一方で、並列接続された複数のディスクリートIGBTを単一の電源で駆動させるため、電源容量を大きくする必要があります。

また、並列接続された各ディスクリートIGBTのエミッタ部がゲート駆動回路内部で共通になり閉ループが出来るので、スイッチング時にゲート電圧の変動が誘起され、IGBTが誤動作する可能性があります。実例として寄生振動を起こしたターンオン波形を図8-8に示し、寄生振動の発生メカニズムを下記に示します。図8-8の $L_{E1}$ と $L_{E2}$ にバラツキがある場合、配線インダクタンス差とIGBTの入力容量により横流が発生し、 $L_{E3}$ と $L_{E4}$ に起電力が発生することで、ゲート電圧が寄生振動することがあります。

共通ドライバ方式の駆動回路を使用する際は、ゲート回路にコモンモードチョークコイルやエミッタ側に抵抗 $R_E$ を挿入するなどの対策を検討し、上記の問題が発生しないことを確認してください。

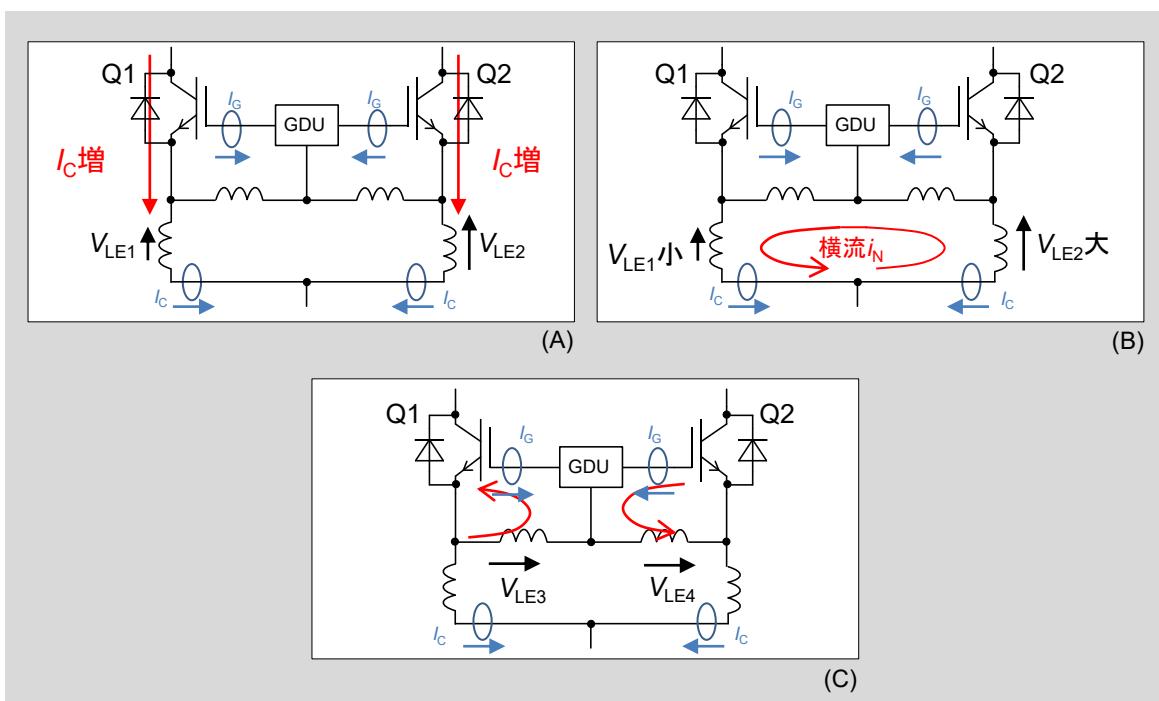

#### 共通ドライバ方式におけるターンオン時の寄生振動メカニズム

- (A)  $Q_1$ と $Q_2$ のIGBTがターンオンすることにより、 $I_C$ が増加し主回路に $dI/dt$ が発生する。これにより配線インダクタンスに起電力 $V_{LE1}$ 、 $V_{LE2}$ が発生する。

- (B) 配線インダクタンスに差がある時、起電力 $V_{LE1}$ と $V_{LE2}$ の大きさに差異があるので、閉ループに横流 $i_N$ が発生する。

- (C) 横流 $i_N$ によりGDU-エミッタ間の配線インダクタンス $L_{E3}$ と $L_{E4}$ に起電力 $V_{LE3}$ と $V_{LE4}$ が発生し、これにより $Q_1$ と $Q_2$ への充放電電流によりゲート電圧の寄生振動が発生する。

図8-8 寄生振動メカニズム

### 3.2.2 並列駆動における個別ゲート駆動回路について

個別ドライバ方式の特長として、並列接続された各ディスクリートIGBTのエミッタ部が共通にならず閉ループが出来ないので、エミッタ部に横流が発生せず、図8-8で示した寄生振動のような誤動作リスクが減ります。一方で、並列接続されたディスクリートIGBTに対し個別のゲート駆動回路を配置するためゲート駆動回路が複雑化します。また、ゲート駆動回路に搭載されるフォトカプラなどの電子部品の特性バラツキによって、並列接続された各ディスクリートIGBTにオン/オフのタイミング差が発生し、スイッチング時に電流アンバランスもしくは誤動作の可能性が生じます。したがって、個別ドライバ方式のゲート駆動回路を設計する際は、各ディスクリートIGBTのオン/オフのタイミング差を限りなく小さくする必要があるため、電子部品の特性ばらつきを考慮してください。

### 3.2.3 共通ドライバ方式におけるゲート抵抗の接続方法

並列接続時に共通ドライバ方式で構成する場合のゲート抵抗の構成は図8-9に示す様に3つの方式があります。

(a)の個別ゲート抵抗方式の場合、各ディスクリートIGBTに接続されているゲート抵抗により、ゲート回路配線の回路インダクタンスとIGBTの入力容量による寄生振動を抑制することができます。しかし、各ディスクリートIGBTを同一のドライバICに接続しても、各ゲート抵抗のバラツキにより、スイッチング時の各IGBTのオン/オフのタイミング差が大きくなることがあります。電流アンバランスや誤動作の可能性があります。

(b)の共通ゲート抵抗方式の場合、各ゲート抵抗値の差がなくなるので、各IGBTのオン/オフのタイミング差を最小にすることが出来ます。しかし、ゲート回路配線の回路インダクタンスとIGBTの入力容量のLC共振により、ゲート電圧の立ち上がり時に寄生振動を起こす場合がありますので注意が必要です。

電圧の寄生振動やIGBTのオン/オフのタイミング差が生じないことを確認すれば、共通ゲート抵抗方式もしくは個別ゲート抵抗方式の適用は可能です。しかし、新規でドライバ回路を設計する場合は、双方の特長を備えた共通ゲート抵抗方式と個別ゲート抵抗方式を組み合わせた(c)のコンビネーションゲート抵抗方式を適用することを推奨します。

図8-9 共通ドライバ方式におけるゲート抵抗の接続方法

## 4. 放熱設計

ディスクリートIGBTを同一のヒートシンク上に搭載して並列接続させて使用する場合、各ディスクリートIGBTの熱干渉を考慮する必要があります。この熱干渉によってチップ接合温度  $T_{vj}$  が高くなると、絶対最大定格温度を超えてディスクリートIGBTが熱破壊する可能性があります。したがって、並列接続時には各ディスクリートIGBT間の熱干渉を考慮し、接合温度  $T_{vj}$  が低くなるように、下記に示す様な点に注意して、並列接続時の放熱設計を行ってください。

- ・各ディスクリートIGBT同士の間隔を十分にとって設置すること

- ・各ディスクリートIGBTの冷却条件を均等にすること

- ・各ディスクリートIGBTに塗布するサーマルグリスを適切な厚さにすること