## ディスクリートIGBT

### Application Manual

注意

1. この資料の内容(製品の仕様、特性、データ、材料、構造など)は2025年12月現在のものです。この内容は製品の仕様変更のため、または他の理由により事前の予告なく変更されることがあります。この資料に記載されている製品を使用する場合には、その製品の最新版の仕様書を入手して、データを確認してください。

2. 本資料に記載してある応用例は富士電機製品を使用した代表的な応用例を説明するものであり、本資料によって工業所有権、その他権利の実施に対する保証または実施権の許諾を行うものではありません。

3. 富士電機は絶えず製品の品質と信頼性の向上に努めています。しかし、半導体製品は故障が発生したり、誤動作する場合があります。富士電機製半導体製品の故障または誤動作が、結果として人身事故、火災等による財産に対する損害や、社会的な損害を起こさないように冗長設計、延焼防止設計、誤動作防止設計などの安全確保をお客様の責任において行ってください。

4. 本資料に記載している製品は、普通の信頼度が要求される下記のような電子機器や電気機器に使用されることを意図して造られています。

- ・コンピュータ・OA機器・通信機器(端末)・計測機器・工作機械

- ・オーディオビジュアル機器・家庭用電気製品・パーソナル機器・産業用ロボットなど

5. 本仕様書に記載されている製品は、人命に関わるような状況下で使用される機器あるいはシステムに用いられる事を目的として設計・製造されたものではありません。以下に示す機器あるいはシステムへの適用に関し、富士電機は一切の責任を負いません。

- ・幹線用通信機器・交通信号機・医療機器

- ・ガス警報器および遮断機・防災/防犯装置・安全確保のための各種装置

6. 極めて高い信頼度を要求される下記のような機器および戦略物資に該当する機器には、本仕様書に記載の製品を使用しないでください。

- ・車両機器(自動車、鉄道、船舶など)・宇宙機器・航空機搭載用機器

- ・原子力制御機器・海底中継機器

7. 本資料の一部または全部の転載複製については、文書による弊社の承諾が必要です。

8. 本資料の内容にご不明の点がありましたら、製品を使用する前に富士電機(株)または、その販売店へ質問してください。本注意書きの指示に従わないために生じたいかなる損害も富士電機(株)とその販売店は責任を負うものではありません。

## 目 次

|                     |      |

|---------------------|------|

| <b>第1章 構造と特長</b>    | 1-1  |

| 1. 素子構造の変遷          | 1-2  |

| 2. ディスクリートIGBTの構造   | 1-4  |

| 3. ディスクリートIGBTの回路構成 | 1-5  |

| 4. TO-247-4の特長      | 1-6  |

| 5. 製品型式の読み方         | 1-9  |

| 6. 製品の刻印について        | 1-10 |

| 7. RoHS指令について       | 1-11 |

| <br>                |      |

| <b>第2章 用語と特性</b>    | 2-1  |

| 1. 用語説明             | 2-2  |

| 2. ディスクリートIGBTの特性   | 2-5  |

| <br>                |      |

| <b>第3章 適用上の注意事項</b> | 3-1  |

| 1. ディスクリートIGBTの選定   | 3-2  |

| 2. 静電気破壊防止対策        | 3-3  |

| 3. 作業環境             | 3-4  |

| 4. ゲート保護            | 3-5  |

| 5. 保護回路の設計          | 3-5  |

| 6. 放熱設計             | 3-6  |

| 7. ゲート駆動回路の設計       | 3-6  |

| 8. 並列接続             | 3-6  |

| 9. TO-247-4の適用      | 3-7  |

| 10. 実装上の注意事項        | 3-8  |

| 11. はんだ付け           | 3-9  |

| 12. 洗浄              | 3-9  |

| 13. 端子の加工、取り付け      | 3-10 |

| 14. 保管              | 3-11 |

| 15. 運搬              | 3-11 |

| 16. 使用上の注意事項        | 3-12 |

|                             |            |

|-----------------------------|------------|

| <b>第4章 トラブル発生時の対処方法</b>     | <b>4-1</b> |

| 1. トラブル発生時の対処方法             | 4-2        |

| 2. 故障判定方法                   | 4-7        |

| 3. 代表的なトラブルと対処方法            | 4-9        |

| <hr/>                       |            |

| <b>第5章 保護回路設計方法</b>         | <b>5-1</b> |

| 1. 短絡(過電流)保護                | 5-2        |

| 2. 過電圧保護                    | 5-8        |

| <hr/>                       |            |

| <b>第6章 放熱設計方法</b>           | <b>6-1</b> |

| 1. ディスクリートIGBTの発生損失         | 6-2        |

| 2. Fuji IGBTシミュレータについて      | 6-3        |

| 3. 昇圧チョッパ回路の発生損失計算方法        | 6-4        |

| 4. 三相2レベルインバータ回路の発生損失計算方法   | 6-5        |

| 5. 放熱の考え方                   | 6-9        |

| <hr/>                       |            |

| <b>第7章 ゲート駆動回路設計方法</b>      | <b>7-1</b> |

| 1. ゲート駆動条件と主要特性の関係          | 7-2        |

| 2. ゲート駆動電流について              | 7-6        |

| 3. デッドタイムの設定                | 7-7        |

| 4. ゲート駆動回路設計の具体例            | 7-9        |

| 5. ゲート駆動回路設計、実装上の注意事項       | 7-10       |

| <hr/>                       |            |

| <b>第8章 ディスクリートIGBTの並列接続</b> | <b>8-1</b> |

| 1. ディスクリートIGBTの選定           | 8-2        |

| 2. 主回路の設計                   | 8-6        |

| 3. ゲート駆動回路の設計               | 8-8        |

| 4. 放熱設計                     | 8-11       |

| <hr/>                       |            |

| <b>第9章 評価・測定方法</b>          | <b>9-1</b> |

| 1. 測定方法                     | 9-2        |

| 2. 電圧の測定                    | 9-3        |

| 3. 電流の測定                    | 9-5        |

## 第1章 構造と特長

|                     |      |

|---------------------|------|

| 1. 素子構造の変遷          | 1-2  |

| 2. ディスクリートIGBTの構造   | 1-4  |

| 3. ディスクリートIGBTの回路構成 | 1-5  |

| 4. TO-247-4の特長      | 1-6  |

| 5. 製品型式の読み方         | 1-9  |

| 6. 製品の刻印について        | 1-10 |

| 7. RoHS指令について       | 1-11 |

無停電電源装置やPVインバータ、急速充電器などに用いられるIGBT(JEDEC登録名称: Insulated Gate Bipolar Transistor)は近年の省エネや装置の小型・軽量化に対する要求の高まりとともに急速な発展を遂げています。このIGBTはパワーMOSFETの高速スイッチング性能とバイポーラトランジスタの高電圧・大電流処理能力を合わせ持った素子として、今後一層の発展が期待されています。

## 1. 素子構造の変遷

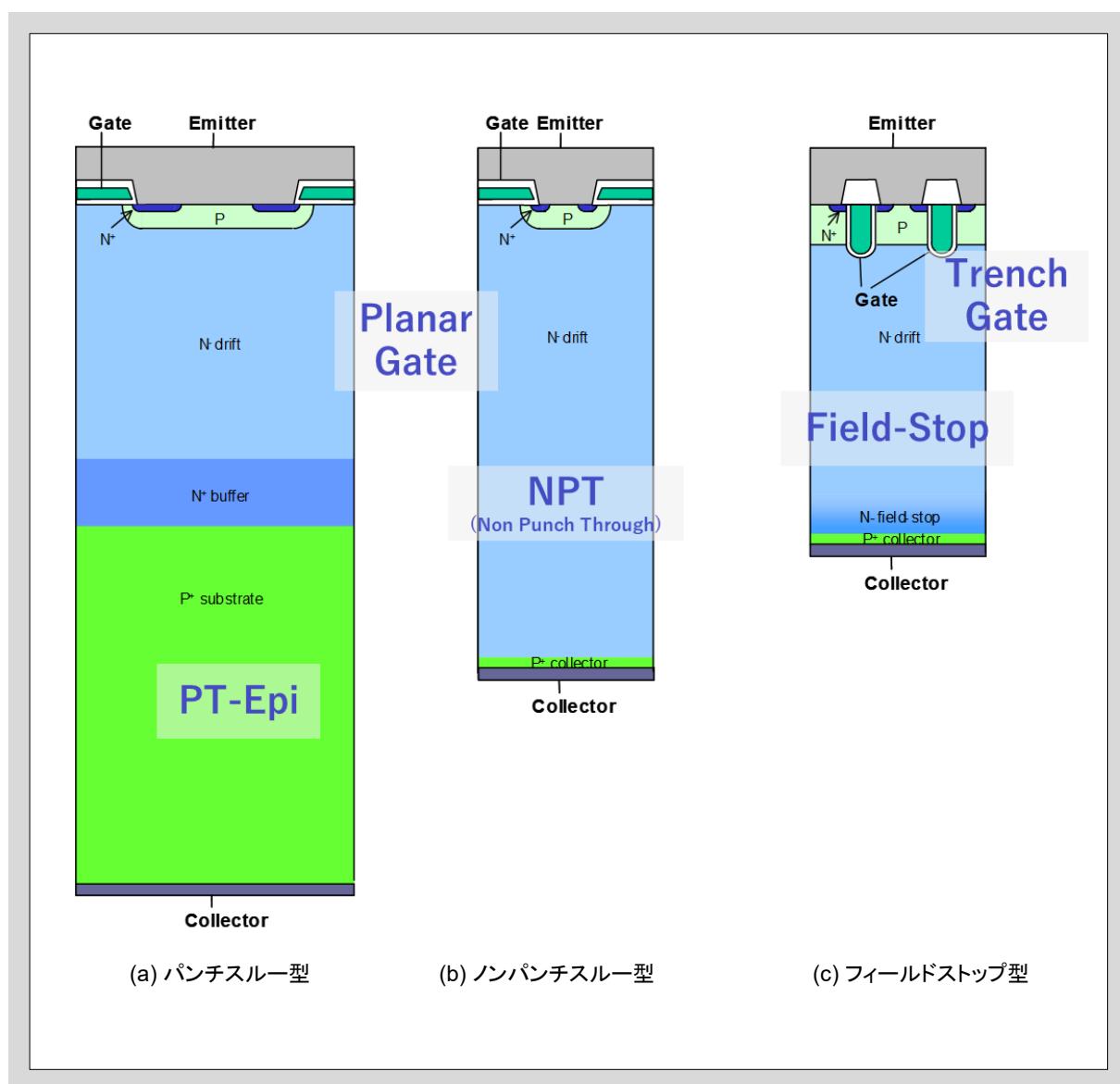

ゲートに正の電圧を印加するとn型チャネルを形成する(nチャネル型)IGBTは、パワーMOSFETのドレイン側のn+層をp+層で置換した構造となっており、nドリフト層の伝導度変調により大電流での低抵抗化が可能なバイポーラ素子です。

IGBTの構造は、表面のゲート構造、nドリフト層を形成するバルク構造、裏面構造に大別することができます。表面のゲート構造はウェーハ表面、すなわちチップ表面にゲートを形成するプレーナゲート構造と、ウェーハ中に溝を掘ってゲートを形成するトレンチゲート構造の2種類があります。一方、バルク構造はオフ時に空乏層がコレクタ側(p-collector層)に到達するパンチスルー(Punch Through)型、到達しないノンパンチスルー(Non Punch Through)型に大きく分けることができます。図1-1にnチャネル型IGBTの構造比較を示します。

富士電機はディスクリートIGBTの製品化を1987年から始め、市場に供給してきました。当時のIGBTは、プレーナゲート構造パンチスルー型IGBTが主流であり、エピキャシタルウェーハを用いて、コレクタ層側から少数キャリアを高注入して伝導度変調効果を得ることで低オン電圧を実現していました。同時にターンオフ時は、nドリフト層の過剰キャリアを速やかに消滅する必要があるため、キャリアライフタイムコントロール技術を適用していました。これにより低オン電圧と高速スイッチングを両立させ、その結果、低いスイッチング損失を実現させていました。このキャリアライフタイムコントロール技術による注入キャリア制御は、IGBTの製造プロセスにとって比較的容易に導入が可能であったため幅広く適用されていました。しかし、オン電圧のばらつきが大きく、また出力特性が負の温度特性を示す等の課題がありました。このため、IGBTの大容量化、それらを用いた電力変換装置の大型化に伴い、より並列接続が容易な特性への要求が高まりました。

これらの課題を開拓するために、ノンパンチスルー型IGBTが開発されました。ノンパンチスルー型IGBTは、コレクタ(p-collector層)の不純物濃度により、少数キャリアの注入効率を制御抑制するとともに、nドリフト層の厚さと抵抗率で内部電界と輸送効率を制御しています。ノンパンチスルー型IGBTではエピタキシャルウェーハを用いず、FZ(Floating Zone)ウェーハを用います。このため、エピタキシャルウェーハと比較した場合のFZウェーハの優位性をIGBTチップに反映できるといった利点があります。例えば、FZウェーハのキャリアライフタイムは非常に長く、IGBTチップの過剰キャリア分布制御は、p-collector層からの少数キャリア注入のみを考慮すればよくなること、オン電圧をはじめとした諸特性ばらつきが、大幅に改善すること、などの利点を持っています。

一方、低オン電圧を達成するためには高輸送効率化する必要があり、nドリフト層を薄くする特別な製造技術が必要でした。そこで富士電機ではウェーハの薄厚化技術を開発し特性改善に貢献してきました。

更なる特性改善のためには、より薄いチップ厚のIGBTが必要となります。チップ厚の大部分をnドリフト層の厚さが占めるため、厚さを薄くしすぎると所定の電圧の保持が不可能になります。この特性改善を阻む要因を打破した構造がFS(Field Stop)構造です。FS構造とはnドリフト層下部に濃度が高いFS層を設けた構造です。この構造を採用することで更なる薄チップ化と特性改善が可能となりました。

また富士電機はIGBTの特性改善に不可欠な技術として表面構造の微細化も併せて進めてきました。IGBTはセルと呼ばれるIGBTの基本構造を多数配置した構造によって形成しています。IGBTセル数が多いほど低オノン電圧化が実現できます。セル高密度化のためウェーハ表面に平面的にIGBTセルを作るプレーナ構造からウェーハ表面にトレンチ(溝)を形成し3次元的にゲートを形成するトレンチ構造へと表面構造も移り変わってきました。このように、バルク構造、表面構造に様々な技術を適用することで特性改善を図ってきました。

図1-1 IGBTの構造比較

## 2. ディスクリートIGBTの構造

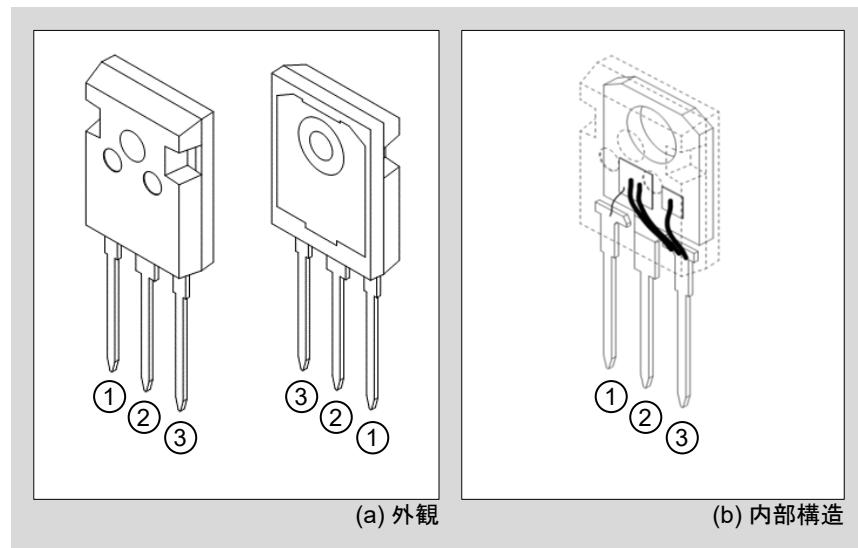

図1-2にIGBTとFWDが内蔵されたTO-247の製品構造を示します。図1-2(a)に外観、図1-2(b)に内部構造を示します。端子先端の①、②、③はそれぞれゲート、コレクタ、エミッタを示しています。ディスクリートIGBTは一般的なIGBTモジュールと異なり、絶縁基板を使用していません。

図1-2 ディスクリートIGBTの構造図

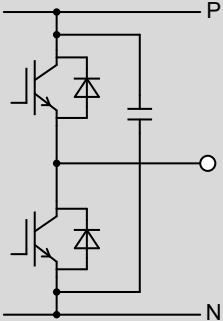

### 3. ディスクリートIGBTの回路構成

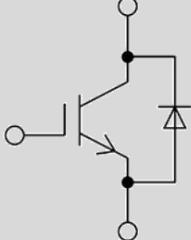

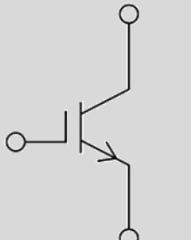

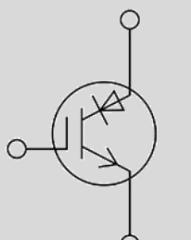

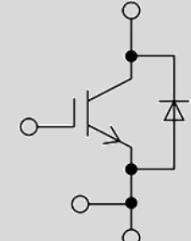

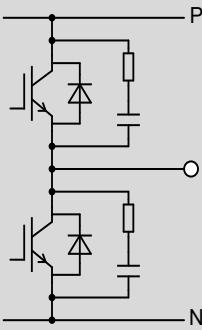

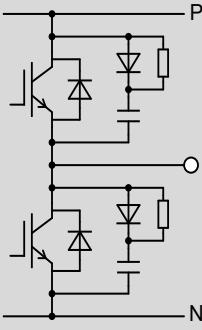

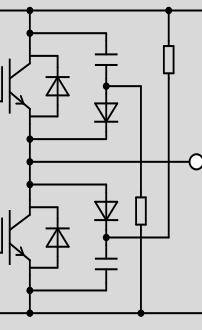

表1-1にディスクリートIGBTの回路構成を示します。

表1-1 ディスクリートIGBTの回路構成例

| パッケージ名称  | 外観                                                                                  | 等価回路                                                                                | 特長                                                                                          |

|----------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| TO-247   |   |    | パッケージの中に逆並列接続したIGBTとFWDを内蔵した製品。PWMインバータの2レベル回路や3レベル回路、チョッパ回路など幅広いアプリケーションで使用される。            |

|          |                                                                                     |   | パッケージの中にIGBTのみを内蔵した製品。チョッパ回路のようにFWDが不要な場合に使用されることが多い。                                       |

|          |                                                                                     |  | パッケージの中に逆耐圧を有するRB-IGBTを内蔵した製品。双向方向スイッチやPWMインバータの3レベル回路(TタイプNPC)の中間素子として使用される。               |

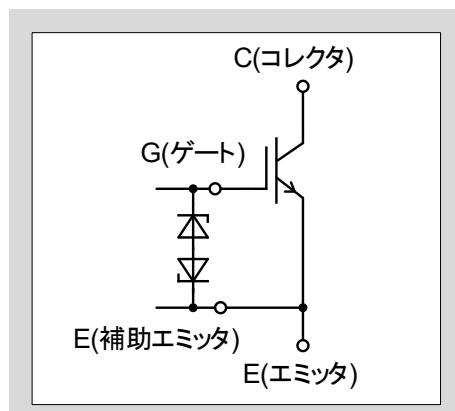

| TO-247-4 |  |  | TO-247にサブエミッタ端子を追加した製品。TO-247と比較してスイッチング損失の低減やゲート電圧のリンギングの抑制ができる。(詳細は4. TO-247-4の特長と第3章を参照) |

## 4. TO-247-4の特長

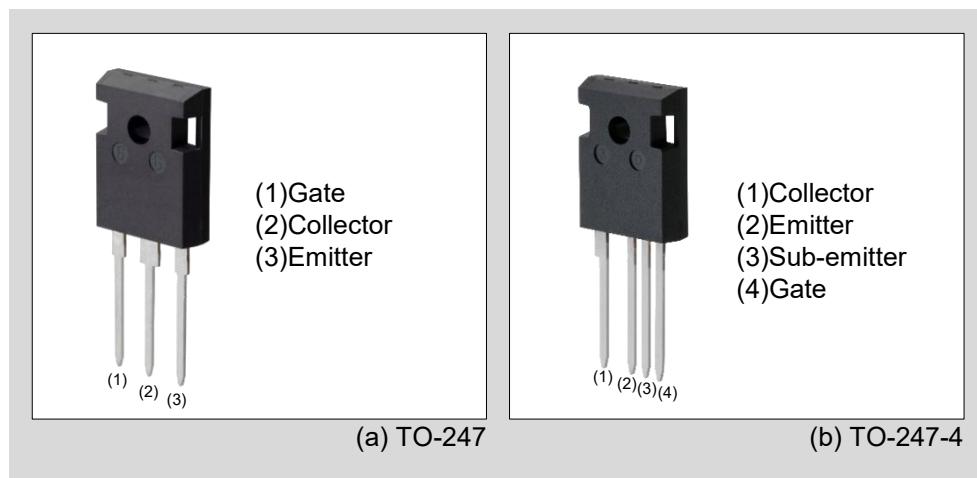

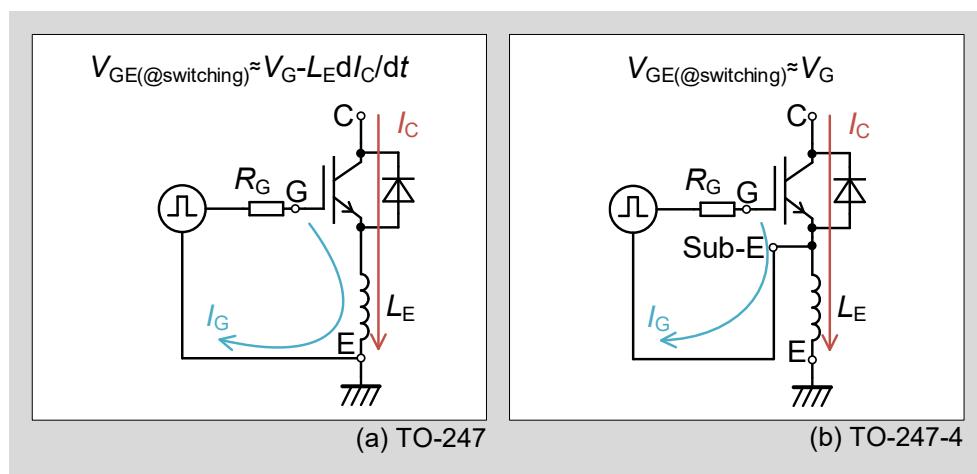

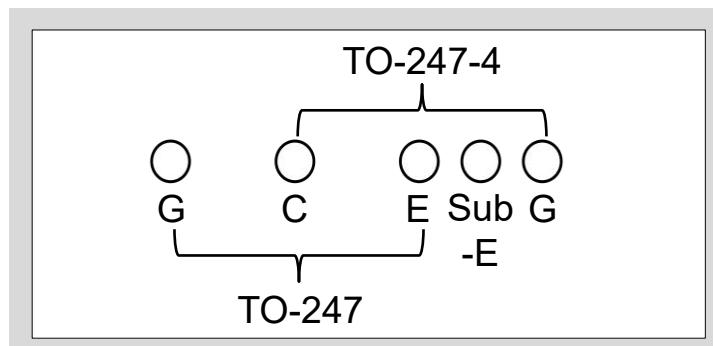

富士電機では図1-3(a)に示すように3端子タイプのTO-247の他に、図1-3(b)に示す4端子タイプのTO-247-4をラインナップしています。

図1-3 パッケージ外観と端子配列

サブエミッタ端子を追加した4端子タイプのTO-247-4では、図1-4に示すようにエミッタ共通のインダクタンス  $L_E$  をゲート駆動回路から分離する接続(ケルビン接続)をすることができます。ケルビン接続をすることで、ゲート駆動回路に発生する電流ループによる誘導起電力  $-L_E \cdot dI_C/dt$  の影響を軽減しています。そのためTO-247と比較して、ゲートの応答性が向上しスイッチング損失(詳細は第2章を参照してください)を低減させることや、ゲート電圧のリングングを抑制することができます。

図1-4 内部回路の概略図

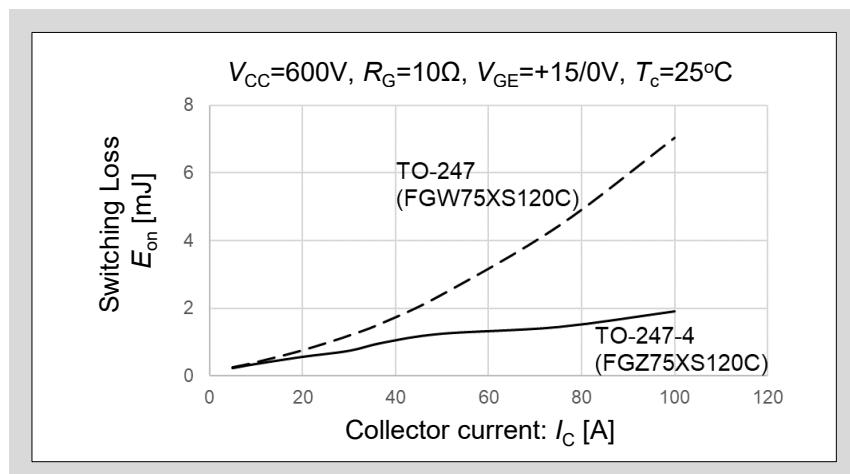

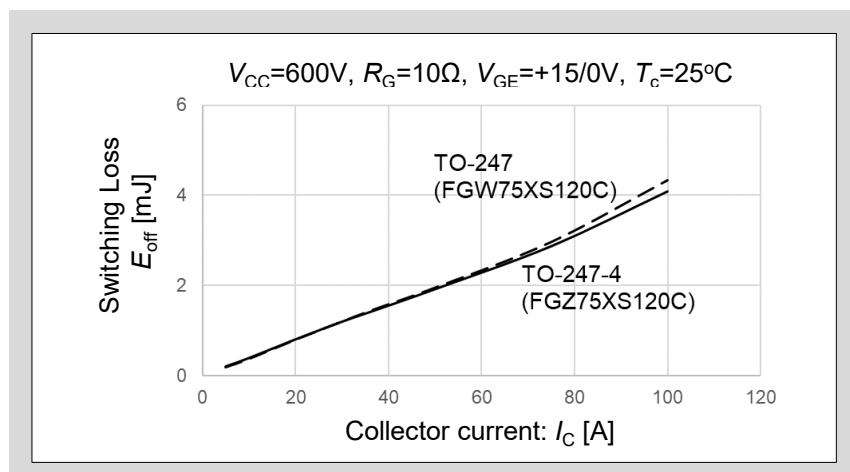

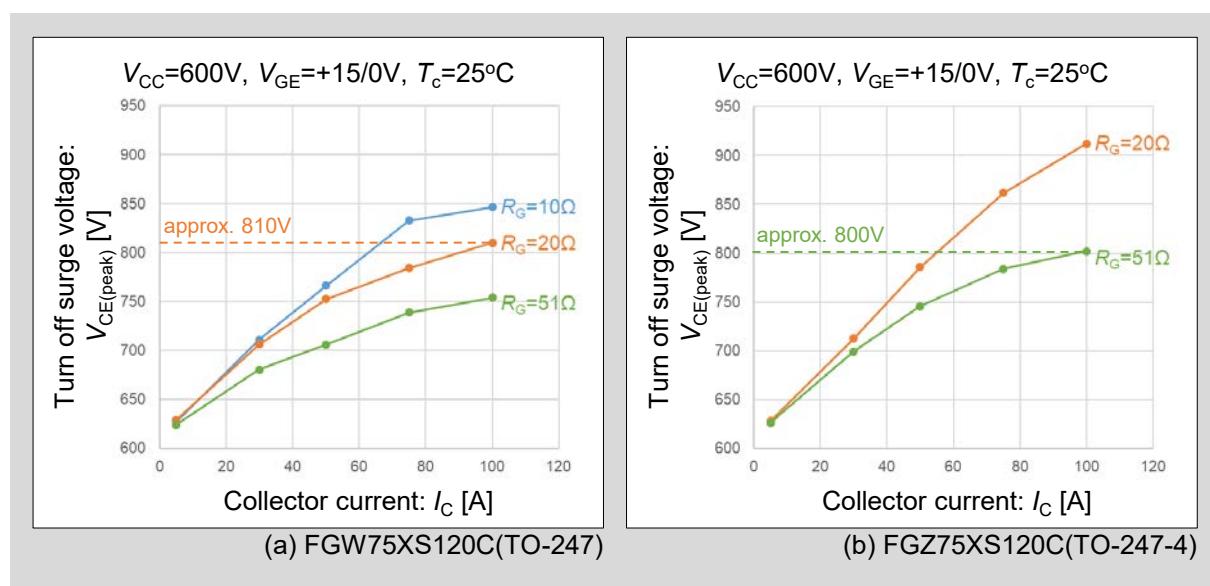

TO-247(FGW75XS120C)と、TO-247-4(FGZ75XS120C)のスイッチング損失の $I_C$ 依存性比較を図1-5と図1-6に示します。これらの図から誘導起電力 $-L_E \cdot dI_C/dt$ の影響が軽減されスイッチング損失が低減できていることが分かります。

図1-5 TO-247とTO-247-4のターンオン損失の比較

図1-6 TO-247とTO-247-4のターンオフ損失の比較

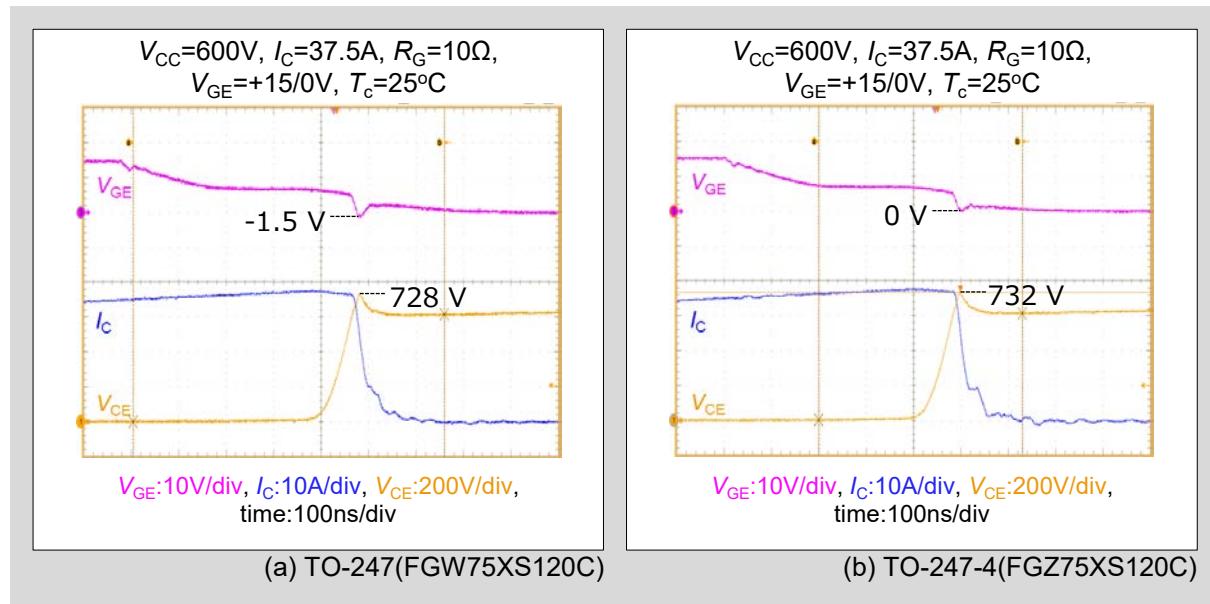

TO-247(FGW75XS120C)と、TO-247-4(FGZ75XS120C)の実際のターンオフ波形を図1-7に示します。この図から、ゲート波形より電流を遮断するときに $V_{GE}$ のリングングが抑制できていることが確認できます。

しかし、TO-247-4は導起電力 $-L_E \cdot dI_C/dt$ の影響を低減することで低損失化やリングングの抑制ができますが、スイッチングスピードが上昇します。このため、TO-247と比較して $dI_C/dt$ が大きくなり、ターンオフ時に発生するサージ電圧が高くなるため注意が必要です。詳細は第3章を参照してください。

図1-7 ターンオフ波形比較

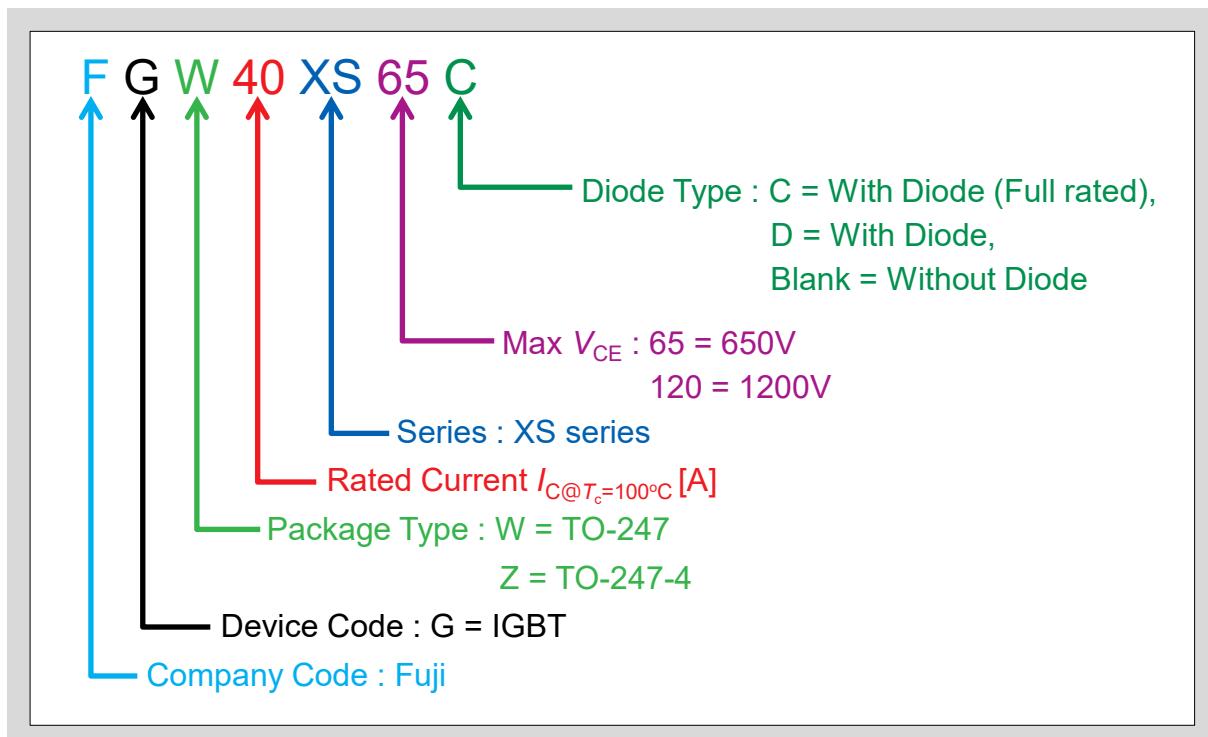

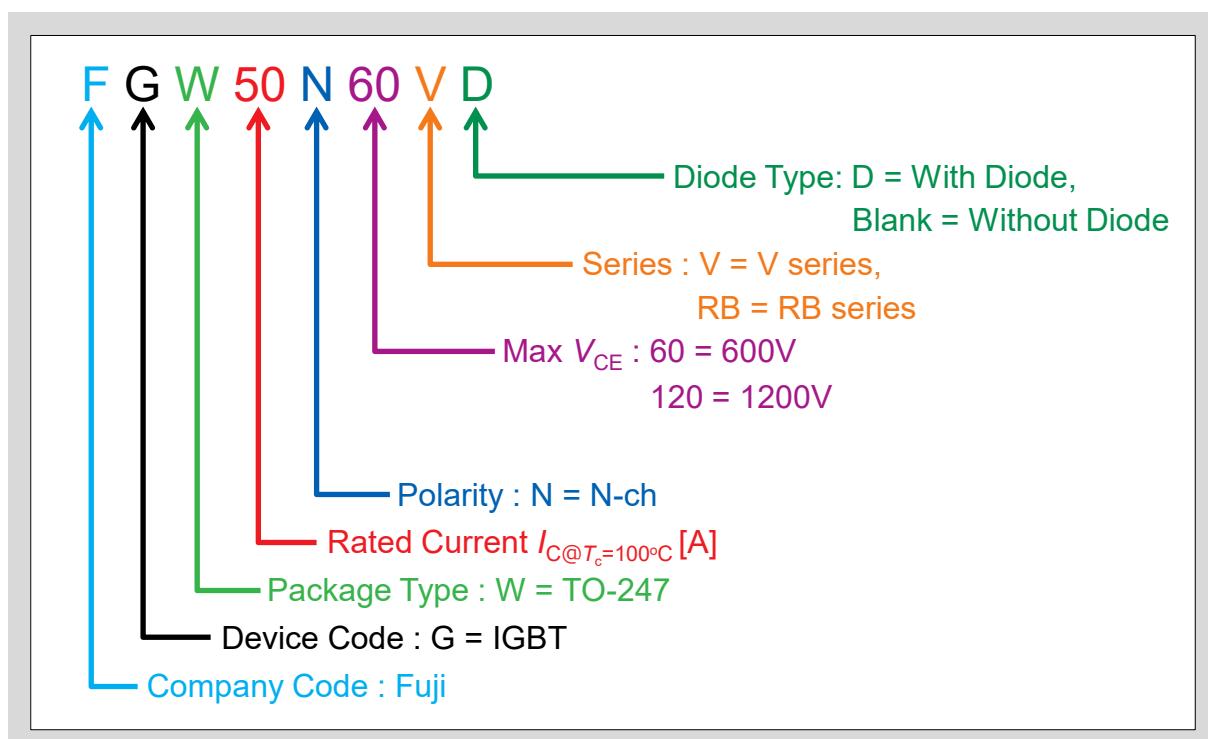

## 5. 製品型式の読み方

図1-8 ディスクリートIGBT XSシリーズの型式の読み方

図1-9 ディスクリートIGBT Vシリーズの型式の読み方

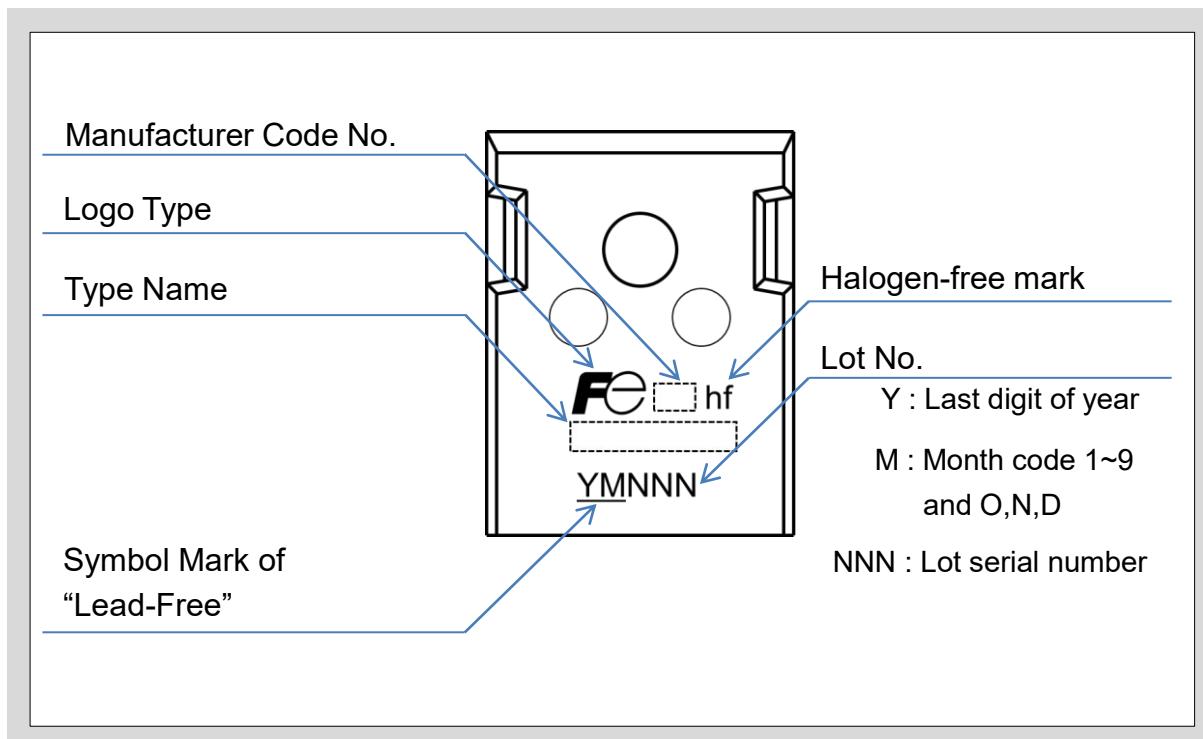

## 6. 製品の刻印について

図1-10 刻印の内容

表1-2 Type Nameの刻印例

| シリーズ | 製品型式        | Type Name |

|------|-------------|-----------|

| XS   | FGW75XS120C | 75XS120C  |

| V    | FGW40N120VD | 40G120VD  |

## 7. RoHS指令について

RoHS(Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment)指令とはEU(欧州連合)が2006年7月1日に施行した有害物質規制のことであり、電気電子機器への特定有害物質の含有を禁止することを示します。

(EU)2015/863で規制対象となっているのは、Pb(鉛)、Cd(カドミウム)、Cr6+(6価クロム)、Hg(水銀)、PBB(ポリブロモビフェニル)、PBDE(ポリブロモジフェニルエーテル)、DEHP (フタル酸ビス(2-エチルヘキシル))、BBP(フタル酸ブチルベンジル)、DBP( フタル酸ジブチル)、DIBP(フタル酸ジイソブチル)の10物質です。

これら10物質をしきい値(Cdは0.01%、他は0.1%)を超えて含有する製品はEU内では販売できませんが、技術的に代替が困難な用途については、適用除外が認められています。

弊社のディスクリートIGBT製品はRoHS指令適合品です。端子部のはんだめっきは、鉛フリーはんだ(Pb 0.1%未満)を使用しております。

## 第2章 用語と特性

|                   |     |

|-------------------|-----|

| 1. 用語説明           | 2-2 |

| 2. ディスクリートIGBTの特性 | 2-5 |

本章では、ディスクリートIGBTに関する用語および特性について説明します。

## 1. 用語説明

以下に、XSシリーズのデータシートに使用している用語について説明します。詳細は納入仕様書をご確認ください。

表2-1 絶対最大定格(Absolute Maximum Ratings)

| 用語                                          | 記号              | 定義および説明(条件は各製品の仕様書を参照してください)                               |

|---------------------------------------------|-----------------|------------------------------------------------------------|

| コレクタ-エミッタ間電圧<br>(Collector-Emitter Voltage) | $V_{CES}$       | ゲート(以下G)-エミッタ(以下E)間を短絡した状態でコレクタ-エミッタ間に印加できる最大電圧            |

| ゲート-エミッタ間電圧<br>(Gate-Emitter Voltage)       | $V_{GES}$       | コレクタ(以下C)-Eを短絡した状態でG-E間に印加できる最大電圧                          |

| コレクタ電流<br>(Collector Current)               | $I_{C@25}$      | $T_c=25^\circ\text{C}$ 時にIGBTに流すことができる最大直流コレクタ電流           |

|                                             | $I_{C@100}$     | $T_c=100^\circ\text{C}$ 時にIGBTに流すことができる最大直流コレクタ電流          |

|                                             | $I_{CP}$        | IGBTに流すことができる最大パルスコレクタ電流                                   |

| 内蔵ダイオード順方向電流<br>(Diode Forward Current)     | $I_{F@25}$      | $T_c=25^\circ\text{C}$ 時に内蔵ダイオード(以下、FWD)に流すことができる最大直流順方向電流 |

|                                             | $I_{F@100}$     | $T_c=100^\circ\text{C}$ 時にFWDに流すことができる最大直流順方向電流            |

|                                             | $I_{FP}$        | FWDに流すことができる最大パルス順方向電流                                     |

| IGBT最大損失<br>(Collector Power Dissipation)   | $P_{tot\_IGBT}$ | $T_c=25^\circ\text{C}$ 時にIGBTで許容する最大電力損失                   |

| 内蔵ダイオード最大損失<br>(FWD Power Dissipation)      | $P_{tot\_FWD}$  | $T_c=25^\circ\text{C}$ 時にFWDで許容する最大電力損失                    |

| 接合部温度<br>(Operating Junction Temperature)   | $T_{vj}$        | 素子が異常を引き起こさず動作できる接合部の最高温度<br>(装置の最悪条件下にて、この値を超えない設計が必要)    |

| 保存温度                                        | $T_{stg}$       | 電極に電気的負荷をかけずに保存、または輸送できる温度範囲                               |

注1:特に規定のない限り $T_{vj}=25^\circ\text{C}$ の値を記載しています。

注2:最大定格として記載されている値は、いかなる場合もこれを超えてはなりません。

表2-2 静特性

| 用語                                                       | 記号            | 定義および説明                                                                                                                       |

|----------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| コレクタ-エミッタ間遮断電流<br>(Zero Gate Voltage Collector Current)  | $I_{CES}$     | G-E間を短絡した状態で、C-E間に指定の電圧を印加したときのC-E間の漏れ電流                                                                                      |

| ゲート-エミッタ間漏れ電流<br>(Gate-Emitter Leakage Current)          | $I_{GES}$     | C-E間を短絡した状態で、G-E間に指定の電圧を印加したときのゲート漏れ電流                                                                                        |

| ゲート-エミッタ間しきい値電圧<br>(Gate-Emitter Threshold Voltage)      | $V_{GE(th)}$  | 指定C-E間電流(以下 $I_C$ )とC-E間電圧(以下 $V_{CE}$ )におけるG-E間電圧(以下 $V_{GE}$ )(C-E間に微小電流が流れ始める $V_{GE}$ 値、IGBTがオンし始める $V_{GE}$ の尺度として用いられる) |

| コレクタ-エミッタ間飽和電圧<br>(Collector-Emitter Saturation Voltage) | $V_{CE(sat)}$ | 指定の $V_{GE}$ において定格の $I_C$ を流した時の $V_{CE}$ 値                                                                                  |

表2-3 動特性

| 用語                                     | 記号           | 定義および説明                                                               |

|----------------------------------------|--------------|-----------------------------------------------------------------------|

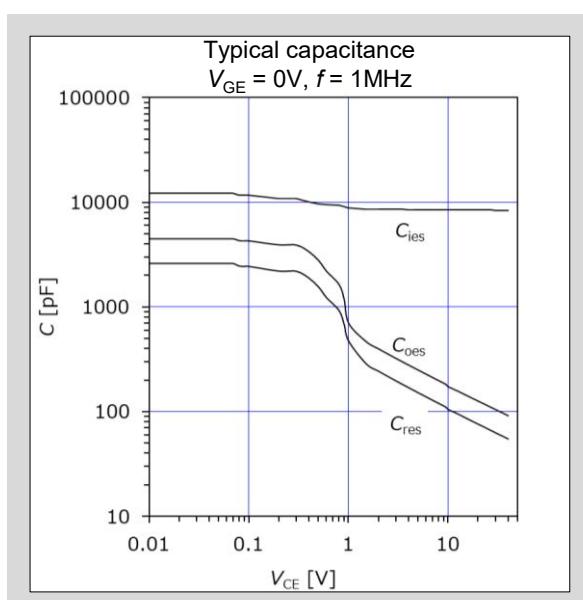

| 入力容量<br>(Input Capacitance)            | $C_{ies}$    | C-E間を交流的に短絡した状態で、G-E間およびC-E間に指定の電圧を印加した時のG-E間容量                       |

| 出力容量<br>(Output Capacitance)           | $C_{oes}$    | G-E間を交流的に短絡した状態で、G-E間およびC-E間に指定の電圧を印加した時のC-E間容量                       |

| 帰還容量<br>(Reverse Transfer Capacitance) | $C_{res}$    | G-E間、C-E間を交流的に短絡した状態でG-E間およびC-E間に指定の電圧を印加した時のC-G間容量                   |

| ゲート電荷量<br>(Gate Charge)                | $Q_G$        | $V_{GE}$ を指定された低い値から高い値まで上昇させるために必要な充電電荷量                             |

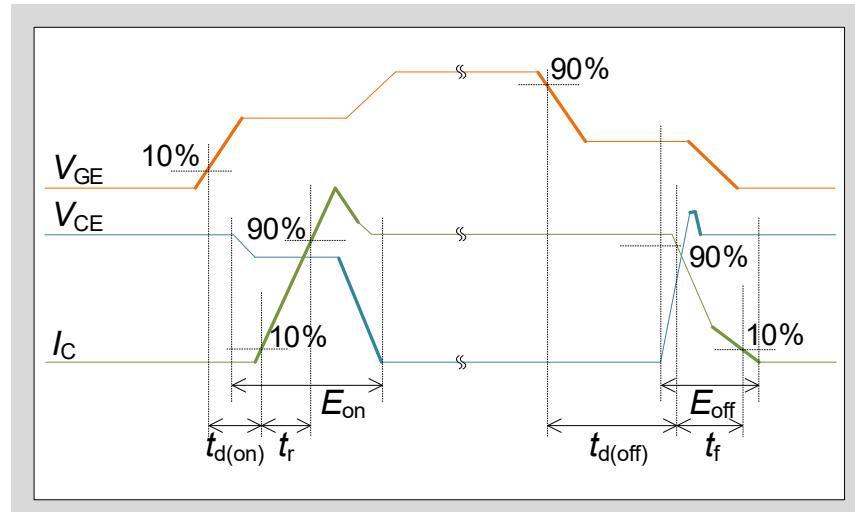

| ターンオン遅れ時間<br>(Turn-On Delay Time)      | $t_{d(on)}$  | IGBTのターンオン時に $V_{GE}$ が最大値の10%に達してから、 $I_C$ が最大値の10%に達するまでの時間(図2-3参照) |

| 立上り時間<br>(Rise Time)                   | $t_r$        | IGBTのターンオン時に、 $I_C$ が最大値の10%に上昇した時点から、最大値の90%に達するまでの時間(図2-3参照)        |

| ターンオフ遅れ時間<br>(Turn-Off Delay Time)     | $t_{d(off)}$ | IGBTのターンオフ時に $V_{GE}$ が最大値の90%に達してから、 $I_C$ が90%に達するまでの時間(図2-3参照)     |

| 立下り時間<br>(Fall Time)                   | $t_f$        | IGBTのターンオフ時に、 $I_C$ が最大値の90%から、10%に下降するまでの時間(図2-3参照)                  |

| ターンオン損失<br>(Turn-On Energy)            | $E_{on}$     | IGBTのターンオン時に発生する損失(図2-3参照)                                            |

| ターンオフ損失<br>(Turn-Off Energy)           | $E_{off}$    | IGBTのターンオフ時に発生する損失(図2-3参照)                                            |

表2-4 FWD特性

| 用語                                        | 記号       | 定義および説明                                                   |

|-------------------------------------------|----------|-----------------------------------------------------------|

| ダイオード順電圧<br>(Forward Voltage Drop)        | $V_F$    | FWDに指定の順方向電流を流したときの順方向電圧                                  |

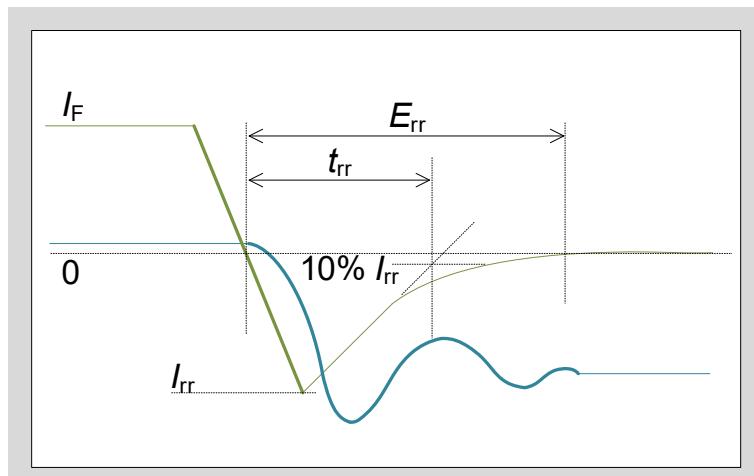

| 逆回復時間<br>(Diode Reverse Recovery Time)    | $t_{rr}$ | FWDのターンオフ時に、電流が0Aを横切った時点から、逆回復ピーク電流の10%に回復するまでの時間(図2-4参照) |

| 逆回復電荷量<br>(Diode Reverse Recovery Charge) | $Q_{rr}$ | FWDの逆回復電流の時間積分値として計算される電荷量                                |

表2-5 熱的特性(Thermal Characteristics)

| 用語                                                               | 記号                   | 定義および説明                      |

|------------------------------------------------------------------|----------------------|------------------------------|

| 素子接合部-周囲間熱抵抗<br>(Thermal Resistance, Junction to Ambient)        | $R_{th(j-a)}$        | ヒートシンクを取付けず無風状態でのチップ-周囲間の熱抵抗 |

| IGBT素子接合部-ケース間熱抵抗<br>(Thermal Resistance, IGBT Junction to Case) | $R_{th(j-c)}_{IGBT}$ | チップ-ケース間の熱抵抗(IGBT)           |

| FWD素子接合部-ケース間熱抵抗<br>(Thermal Resistance, FWD Junction to Case)   | $R_{th(j-c)}_{FWD}$  | チップ-ケース間の熱抵抗(FWD)            |

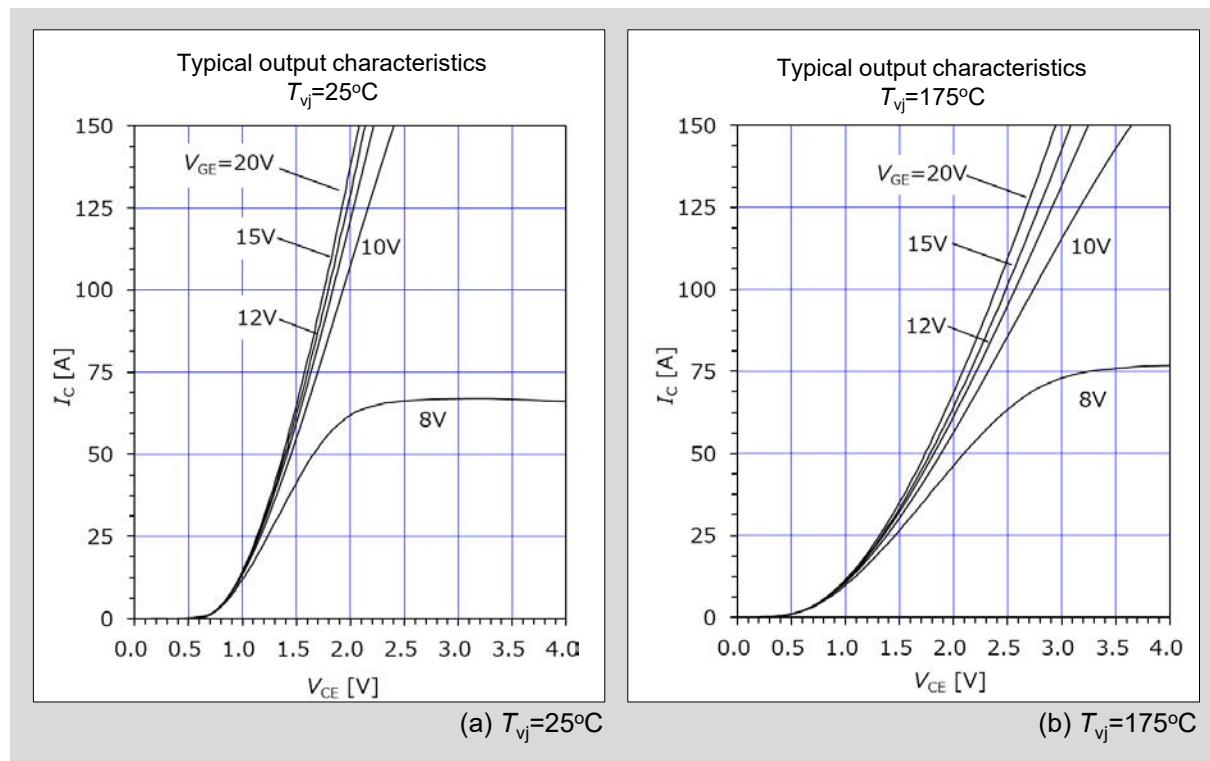

## 2. ディスクリートIGBTの特性

ディスクリートIGBT製品にはIGBTと逆並列にFWDを接続している製品とIGBT単体の製品があります。FGZ75XS120C(1200V/75A素子)を例に、仕様書などに記載しているIGBTとFWDの種々の特性の説明を以下に示します。

### 2.1 静特性

$V_{CE}$ - $I_C$ 特性(一般的に出力特性と呼ばれる) $V_{GE}$ 依存性を図2-1に示します。この特性はIGBTがオンしている時の $V_{CE}$ と $I_C$ の関係を示すもので、オン時にIGBTに発生する損失となります。従って $V_{CE}$ が低い程、発生損失が小さくなります。この特性は $T_{vj}$ と $V_{GE}$ によって変化しますので、これらの特性をよく考慮した上で装置設計を行ってください。

一般的には $V_{GE}=15V$ において、装置の最大出力ピーク電流 $\leq$ 素子の定格電流値で使用することを推奨します。

図2-1  $V_{CE}$ - $I_C$ 特性

## 2.2 スイッチング特性

IGBTは一般的にスイッチング用途に使用するため、ターンオン、ターンオフ時のスイッチング特性を十分に理解しておくことが重要です。また、この特性は種々のパラメータによって変化するため、これらも考慮に入れて装置の設計を行う事が必要です。

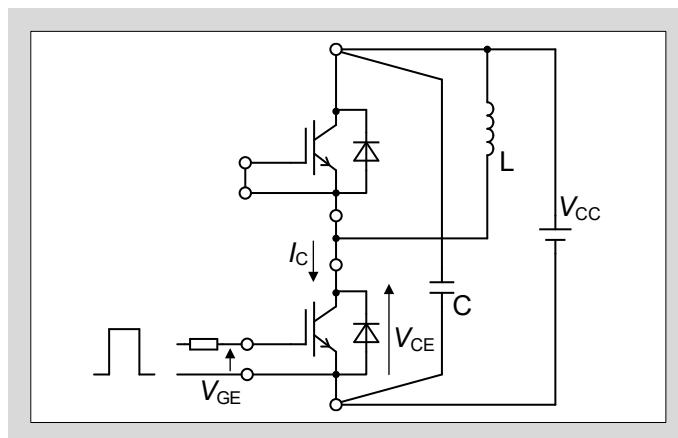

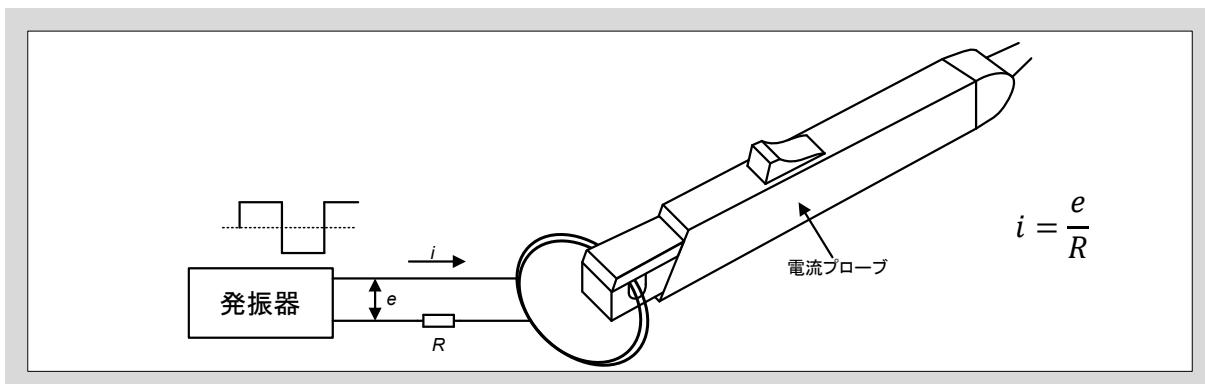

スイッチング特性は、スイッチング時間とスイッチング損失の二つに大別することができます。これらのスイッチング特性は図2-2に示す回路で測定する事が出来ます。

図2-2 スイッチング特性測定回路

表2-3、表2-4に記載した特性 $t_{d(on)}$ 、 $t_r$ 、 $t_{d(off)}$ 、 $t_f$ 、 $E_{on}$ 、 $E_{off}$ 、 $t_{rr}$ に加え、 $E_{rr}$ 、 $I_{rr}$ の定義を図2-3と図2-4の概略波形で示します。

図2-3 スイッチング時間の定義 (ターンオン、ターンオフ波形)

図2-4 スイッチング時間の定義 (逆回復波形)

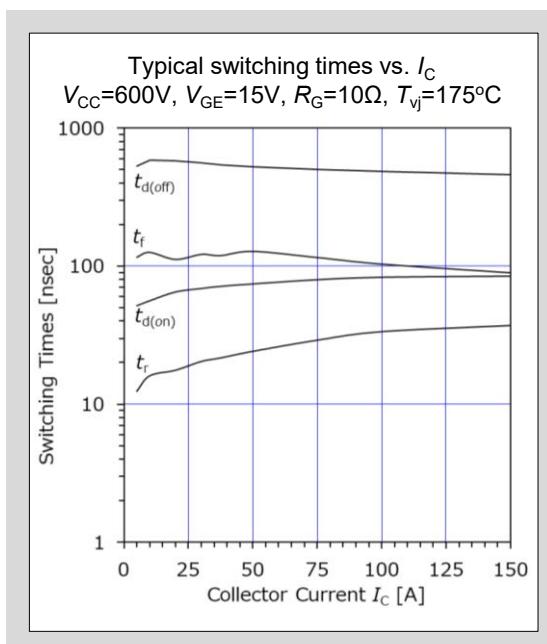

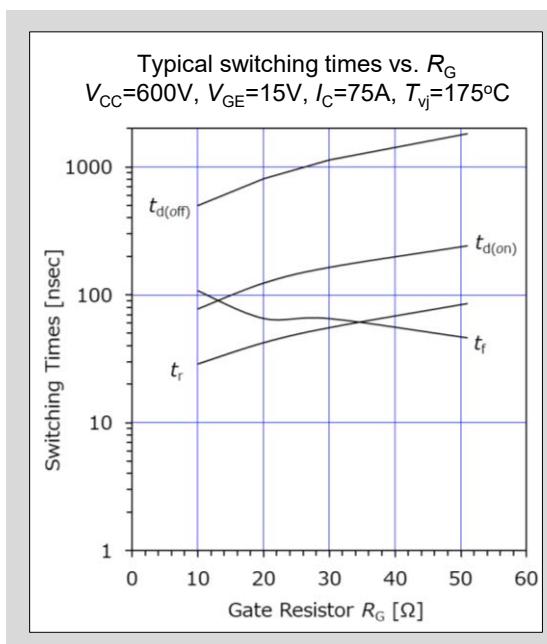

これらのスイッチング時間と $I_C$ の関係を図2-5に示します。また、スイッチング時間とゲート抵抗 $R_G$ の関係を図2-6に示します。スイッチング時間は $I_C$ 、 $T_{vj}$ 、 $R_G$ によって変化しますので装置設計の際は十分に考慮してください。

例えば、 $t_{d(off)}$ や $t_f$ などのスイッチング時間が長くなる条件で使用すると、デッドタイム不足による直列アーム短絡(詳細は第4章を参照してください)などの不具合を起こし素子が破壊する可能性があります。一方、 $t_f$ などのスイッチング時間が短すぎる条件で使用すると過渡的な電流変化 $dI_C/dt$ が大きくなり、回路の浮遊インダクタンスによる過大なサージ電圧(=浮遊インダクタンス・ $dI_C/dt$ )が発生します。このサージ電圧が印加電圧に重畠されるため、RBSOA(詳細は第2、4章を参照してください)を超えて素子が破壊する場合もあります。したがって装置設計時には、 $I_C$ 、 $T_{vj}$ 、 $R_G$ などを十分に考慮し、上記不具合が発生しないように設計する必要があります。

図2-5 スイッチング時間- $I_C$ 特性

図2-6 スイッチング時間- $R_G$ 特性

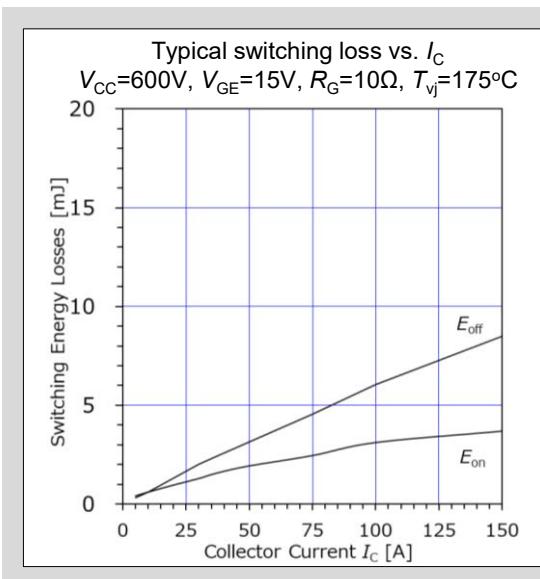

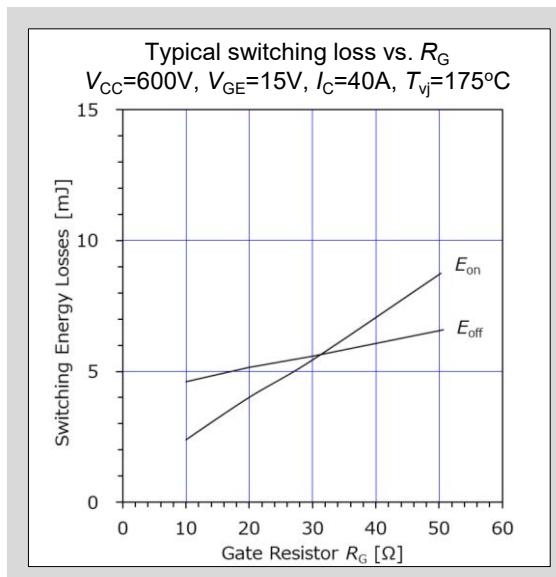

$E_{on}$ 、 $E_{off}$ 、 $E_{rr}$ は、IGBTがスイッチングする際(ターンオン、オフ時)に発生します。この特性は図2-7、図2-8、図2-9に示す様に $I_C$ 、 $T_{vj}$ 、 $R_G$ で変化します。特に $R_G$ の選定は重要で、大きすぎるとスイッチング損失が大きくなる上、前述のデッドタイム不足による直列アーム短絡を起こしやすくなります。逆にスイッチング損失を小さくするために $R_G$ を小さくする場合は、前述の過大なサージ電圧が発生する可能性があります。

$R_G$ の選定においては浮遊インダクタンス $L_S$ が大きく影響します。 $L_S$ が小さければ過大なサージ電圧が発生しにくいので、 $R_G$ 選定の検討が容易になります。したがって装置設計において、この $L_S$ の値を出来るだけ小さく設計する事を推奨します。

なお、 $R_G$ の決定にはIGBT駆動回路の容量とのマッチングも考慮する必要がありますので、本章2.3の容量特性を使用して十分に検討を行った上で $R_G$ を選定してください。

図2-7  $E_{on}$ 、 $E_{off}$ - $I_C$ 特性

図2-8  $E_{on}$ 、 $E_{off}$ - $R_G$ 特性

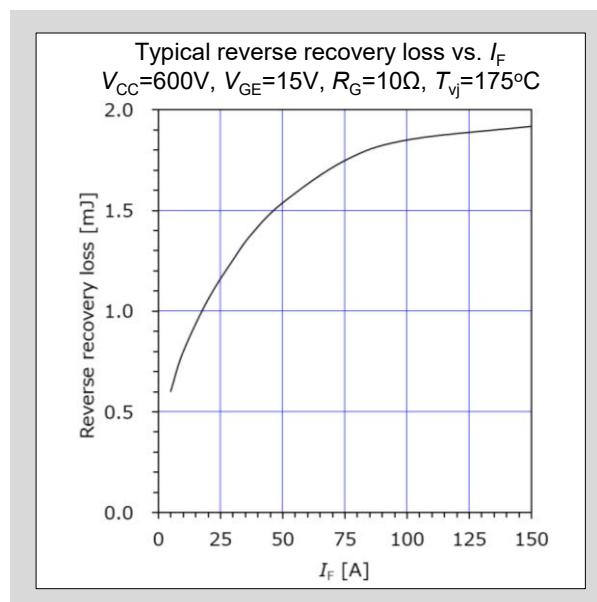

図2-9  $E_{rr}$ - $I_F$ 特性

### 2.3 容量特性

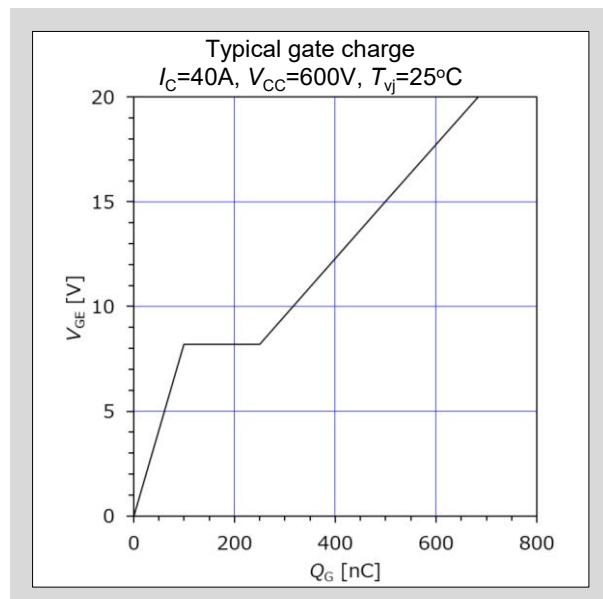

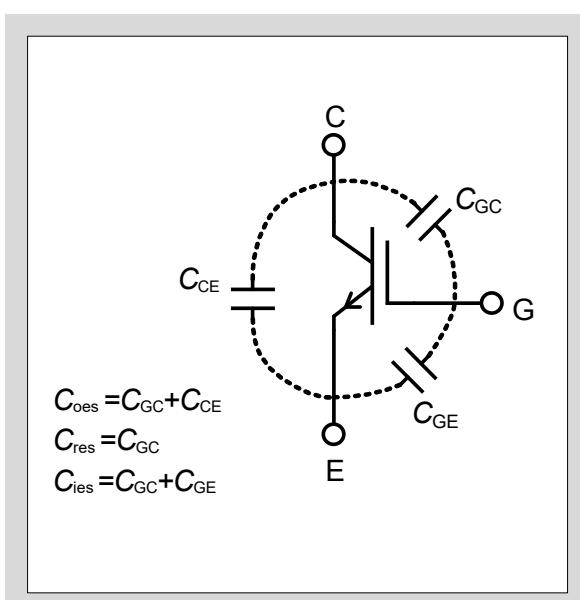

図2-10に $Q_G$ の特性を示します。この特性は、 $Q_G$ に対する $V_{GE}$ の変化を示しています。「 $Q_G$ が増加する」ことは「IGBTのG-E間の容量に電荷を充電する」ことを表すため、 $Q_G$ が増加すると $V_{GE}(=Q_G / G-E間容量)$ が上昇しIGBTがオンします。IGBTがオンすると $V_{CE}$ がオン電圧まで下降します。このように $Q_G$ はIGBTを駆動するために必要な電荷量を示しています。この特性は駆動回路の電源容量を決定する際に使用してください。図2-11にIGBTの各接合容量の特性を示します。また、IGBTの接合容量である $C_{ies}$ 、 $C_{oes}$ 、 $C_{res}$ を図2-12に示します。これらの特性は $Q_G$ と共に駆動回路設計の際に使用してください。

図2-10  $V_{GE}$ - $Q_G$ 特性

図2-11 接合容量- $V_{CE}$ 特性

図2-12 接合容量

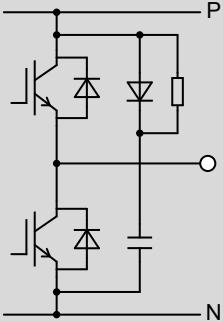

## 2.4 逆バイアス安全動作領域RBSOA

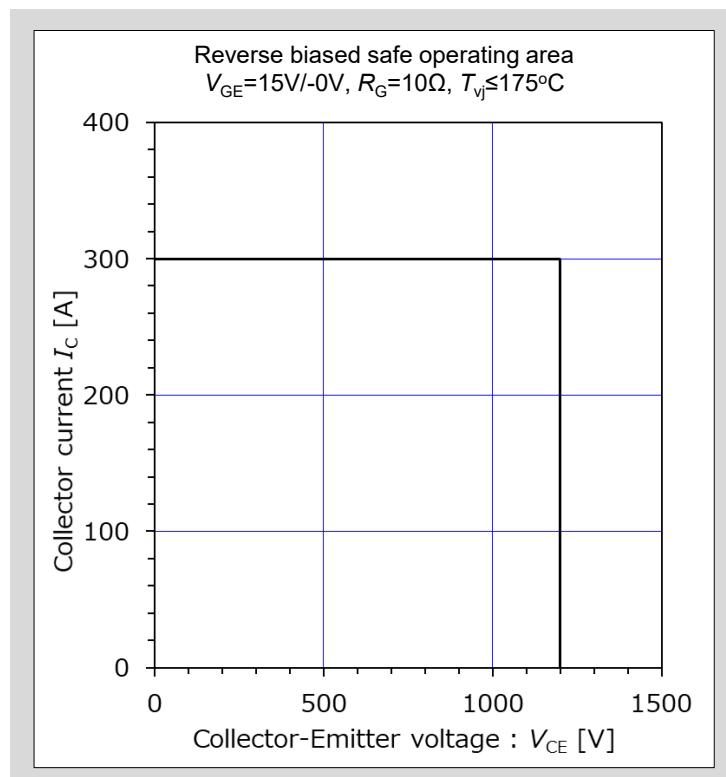

IGBTをターンオフさせる際、安全に遮断できる $V_{CE}$ - $I_C$ の動作範囲を逆バイアス安全動作領域RBSOA(Reverse Bias Safe Operating Area)と言います。図2-13にRBSOAの範囲を示します。ターンオフ時 $V_{CE}$ - $I_C$ の動作軌跡がこのRBSOAの領域に納まるように設計する必要があります。

図2-13 逆バイアス安全動作領域(RBSOA)

## 2.5 FWDの特性

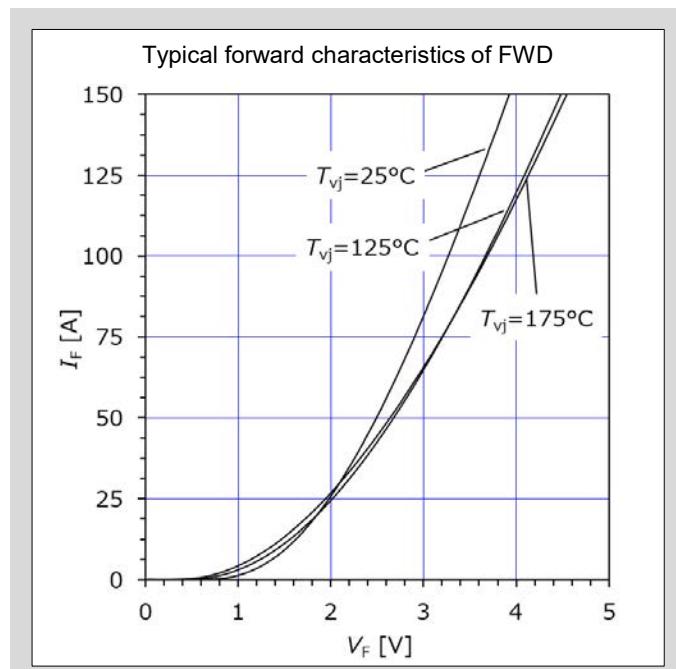

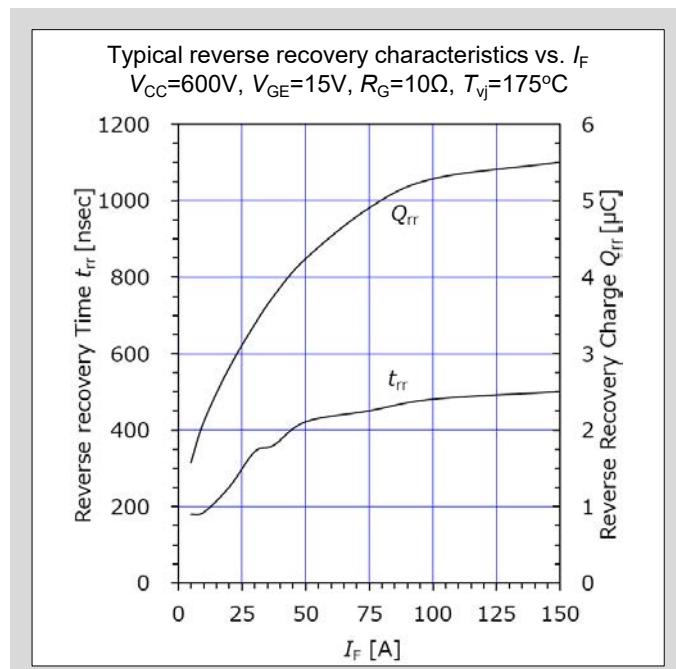

FWDを内蔵しているディスクリートIGBTの場合、FWDには図2-14に示す $V_F$ - $I_F$ 特性と図2-15に示す逆回復特性( $t_{rr}$ 、 $Q_{rr}$ )、および図2-9に示す逆回復動作時の $E_{rr}$ 特性があります。これらの特性はIGBTと同様FWDに発生する損失計算に使用します。またFWDの特性は $I_F$ 、 $T_{vj}$ 、 $R_G$ などで変化するので注意が必要です。

図2-14  $V_F$ - $I_F$ 特性

図2-15  $t_{rr}$ 、 $Q_{rr}$ 特性

## 2.6 過渡熱インピーダンス特性

温度上昇の計算およびヒートシンクの設計に用いる過渡熱インピーダンス特性を図2-16に示します。

この過渡熱インピーダンス特性はIGBT、FWDの $T_{vj}$ を計算する際に使用します。(詳細は第6章を参照して

ください)

図2-16 過渡熱インピーダンス特性

## 第3章 適用上の注意事項

|                   |      |

|-------------------|------|

| 1. ディスクリートIGBTの選定 | 3-2  |

| 2. 静電気破壊防止対策      | 3-3  |

| 3. 作業環境           | 3-4  |

| 4. ゲート保護          | 3-5  |

| 5. 保護回路の設計        | 3-5  |

| 6. 放熱設計           | 3-6  |

| 7. ゲート駆動回路の設計     | 3-6  |

| 8. 並列接続           | 3-6  |

| 9. TO-247-4の適用    | 3-7  |

| 10. 実装上の注意事項      | 3-8  |

| 11. はんだ付け         | 3-9  |

| 12. 洗浄            | 3-9  |

| 13. 端子の加工、取り付け    | 3-10 |

| 14. 保管            | 3-11 |

| 15. 運搬            | 3-11 |

| 16. 使用上の注意事項      | 3-12 |

本章ではディスクリートIGBTの取り扱い時、および装置への適用時の注意点を説明します。

## 1. ディスクリートIGBTの選定

ディスクリートIGBTを使用する場合、どのような電圧・電流定格の素子を選定すれば良いか考慮する必要があります。この節では様々な注意点を項目ごとに分け説明します。

### 1.1 電圧定格

ディスクリートIGBTの電圧定格は、適用する装置の入力電源である商用電源電圧や、装置のDCリンク電圧によって決まります。この関係を表3-1に示しますので、表を参考にして目的に応じた素子を選定してください。

表3-1 ディスクリートIGBTの電圧定格適用例

|         | ディスクリートIGBTの電圧定格 |         |

|---------|------------------|---------|

|         | 650V             | 1200V   |

| 商用電源電圧  | ~240VAC          | ~480VAC |

| DCリンク電圧 | ~520VDC          | ~960VDC |

### 1.2 電流定格

ディスクリートIGBTのコレクタ電流 $I_C$ が大きくなると、発生する導通損失やスイッチング損失が増大し、素子の発熱が大きくなります。IGBT、FWDのチップ接合温度 $T_{vj}$ は最大保証温度以下で使用する必要があるため、最大保証温度を超えないような電流定格を選択してください。この設計を誤ると素子破壊、あるいは長期信頼性の低下を招くことがありますので注意してください。

このような観点から、ディスクリートIGBTの電流定格選定は非常に重要です。また、高周波スイッチング用途ではスイッチング損失の増大(スイッチング回数が多い程、合計のスイッチング損失が大きくなります)により発熱が大きくなるので注意が必要です。

電流定格の基本的な選定基準はIGBTに流れる電流の2~3倍以上を選定するのが一般的です。しかし電流定格の選定に関しては、装置の運転条件や放熱条件にも依存するため、その装置での発生損失と温度上昇を確認した上で、電流定格を選定してください。

### 1.3 最大定格

製品は仕様書に記載されている最大定格(電圧、電流、温度など)の範囲内で使用してください。最大定格を超えて使用すると、製品が破壊する場合があります。また、絶対最大定格の各項目値はそれぞれの項目に対する保証値であり、組み合わせにおける保証をするものではありません。

最大定格内の使用であっても、温度や使用環境により期待する製品寿命が得られない場合があります。製品の絶対最大定格を参照の上、使用されるシステム・装置などへの富士電機製品の適合性は適用側にて評価・検証の上、判断してください。

### 1.4 RBSOA

IGBTのターンオフ電圧・電流の動作軌跡がRBSOA仕様内にあることを確認してください。RBSOAの範囲を超えて使用するとディスクリートIGBTが破壊する可能性があります。

## 2. 静電破壊防止対策

IGBTは、小信号MOSFETや集積回路に比べはるかに大きな静電破壊耐量を持っていますが、これらの製品と同様静電気によって破壊する恐れがあります。

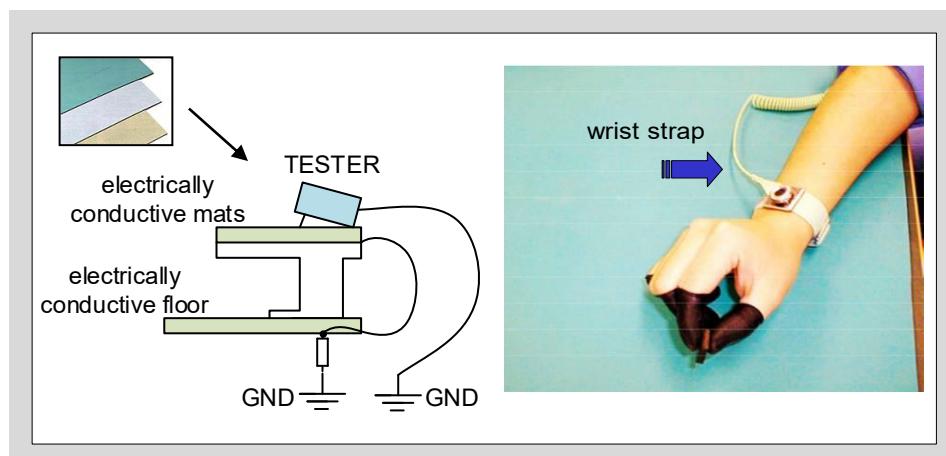

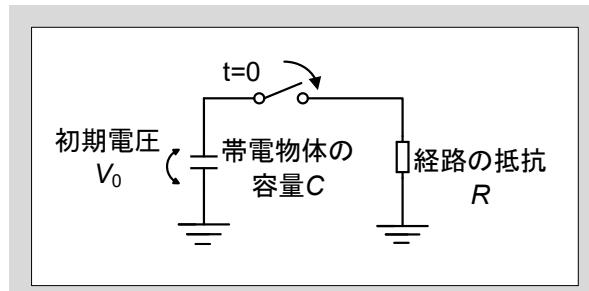

図3-1に示すように、導電体に帯電した静電気は導電性のテーブルマット・リストストラップ・フロアマットを適切に使用することで取り除くことができます。電荷を取り除くスピードは、帯電物体の容量経路の抵抗によって決定します。図3-2に導電体の帯電物体が容量Cを持ち経路抵抗がRの場合の等価回路を示します。また、帯電物体の電圧は時間tの関数として次式のように与えられます。

図3-1 静電気破壊防止対策例

$$V = V_0 \cdot \exp\left(-\frac{t}{RC}\right)$$

V : 時間tにおける帯電物体の電圧 [V]

V<sub>0</sub> : 帯電物体の初期電圧 [V]

t : 時間 [sec]

C : 帯電物体の容量 [F]

R : 経路の抵抗 [Ω]

図3-2 静電気放電の等価回路

<例>

例として、1秒以内に作業者の静電気レベルを100V以下にするときの抵抗の計算方法を示します。

$V = 100\text{V}$  (安全電圧)、 $V_0 = 10\text{kV}$  (人体あるいは帯電物体の初期電圧)、

$t = 1\text{sec}$  (安全電圧100Vを達成するための最長許容時間)、

$C = 200\text{pF}$  (人体の容量100pF~400pFの平均値)、 $R$  = 大地までの最大許容抵抗 [ $\Omega$ ]

以上を代入して

$$100 = 10 \times 10^3 \cdot \exp\left(-\frac{1}{200 \times 10^{-12} \cdot R}\right)$$

したがって  $R \geq 1.09 \times 10^9 \Omega = 1090\text{M}\Omega$  となります。テーブルマット・フロアーあるいはリストストラップから大地までの抵抗が1000MΩ以下であれば安全電圧100Vまでの放電が1秒以内に行われます。

### 3. 作業環境

- 作業を行う人は人体アースを取ってください。人体アースはリストストラップや銅の指輪等を付け、感電防止のため1MΩ程度の抵抗を取付けて、アースに接続してください。

- 作業環境は導通性のフロアマットやテーブルマット等を敷き、アースに接続してください。また、湿度はカーボトレーサーなどの測定器を使用する場合は測定器もアースに接続してください。

- はんだ付けを行う場合ははんだゴテやはんだバスからのリーク電圧がディスクリートIGBTへ印加しないよう、はんだバス等のアースに接続してください。

- 端子に直接触れないよう、パッケージ本体を持って取り扱ってください。

## 4. ゲート保護

絶対最大定格を超える電圧をIGBTのG-E間に印加した場合、IGBTのゲートが破壊する危険があります。このためG-E間には絶対最大定格を超える電圧を印加しないでください。

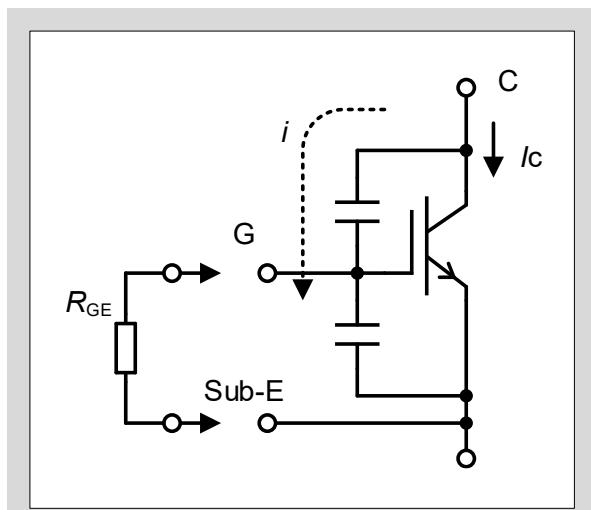

G-E間にオーブン状態でC-E間に電圧を印加すると、IGBTが破壊する可能性があります。これはコレクタ電位の変化により、図3-3に示す電流*i*がコレクタからゲートに流れ、ゲート電位が上昇することでIGBTがオンし*I<sub>C</sub>*が流れる事によってIGBTが発熱する事が原因です。

ディスクリートIGBTを装置に組み込んだ後に、ゲート回路の故障、或いはゲート回路が正常に動作しない状態(ゲートがオーブン状態)で主回路電圧を印加すると上記の理由によりIGBTは破壊することがあります(第7章5.2項参照)。その破壊防止のためにはG-E間に10kΩ程度の抵抗*R<sub>GE</sub>*を接続することを推奨します。

図3-3 G-E間オーブン状態でのIGBTの振る舞い

## 5. 保護回路の設計

ディスクリートIGBTは過電流・過電圧といった異常状態により破壊する可能性があります。したがって、その異常状態から素子を保護するための保護回路設計は非常に重要です。

ディスクリートIGBTを保護する回路は素子特性を十分に理解した上で、素子特性にマッチングするように設計してください。マッチングが取れていないと保護回路が付いていても素子が破壊することがあります。

その一例として、過電流保護をかける時の遮断時間が長いこと、スナバ回路のコンデンサ容量が小さく過大なサージ電圧が発生することなどが挙げられます。これら過電流・過電圧保護方法は、第5章「保護回路設計方法」に詳しく説明していますので、そちらを参照してください。

## 6. 放熱設計

ディスクリートIGBTには、許容できる最大保証温度が定められており、この温度以下になるような放熱設計が必要です。放熱設計を行う際は、適用するアプリケーションの動作を十分に考慮した上で設計してください。

放熱設計を行うためには、まず素子の発生損失を算出し、その損失をもとに許容温度以下となるヒートシンクの選定を行います。放熱設計が十分でない場合、実機運転中に素子の  $T_{vj}$  が最大保証温度を超える可能性があります。注意点などを含め詳しい説明を第6章「放熱設計方法」に記載していますのでそちらを参照してください。

## 7. ゲート駆動回路の設計

素子の性能を十分に引き出すためにはゲート駆動回路の設計が重要です。また、保護回路の設計にも密接に関わってきます。

$dV/dt$  が高いと対向アームIGBTの誤点弧や、ゲート過電圧を起こしたり、電源ラインにノイズが伝搬する可能性があります。誤点弧、ゲート過電圧、予期しない電源ノイズを起こさないための最適なドライブ条件( $+V_{GE}$ 、 $-V_{GE}$ 、 $R_G$ 、 $C_{GE}$ )を検討してください。

ディスクリートIGBTとゲート駆動回路間の配線長が長い場合、製品端子のゲート電圧が過渡的に変動し製品が過電圧破壊する場合があります。ゲート過電圧破壊を防止するために、適切なゲート配線設計とゲート電圧の確認を実施してください。

注意点などを含め詳しい説明を第7章「ゲート駆動回路設計方法」に記載していますのでそちらを参照してください。

## 8. 並列接続

大電流を制御する用途にディスクリートIGBTを適用する場合、素子を並列に接続して使用する場合があります。

並列接続して使用する場合、並列接続した素子に均等な電流が流れよう設計することが重要です。もし電流バランスが崩れた場合、一つの素子に電流が集中し破壊する可能性があります。

並列接続時の電流バランスは、素子特性や配線方法などで変わってくるため、並列接続した各素子のC-E間飽和電圧  $V_{CE(sat)}$  を合わせる、主回路配線を均等にするといった管理・設計が必要になります。注意点などを含め、詳しい説明を第8章「ディスクリートIGBTの並列接続」に記載していますのでそちらを参照してください。

## 9. TO-247-4の適用

TO-247-4は誘導起電力 $-L_E dI_C/dt$ の影響を低減することで低損失化やリンギングの抑制ができますが、スイッチングスピードが上昇します。すなわちTO-247と比較して $dI_C/dt$ が大きくなり、ターンオフ時に発生するサージ電圧が高くなるため注意が必要です。図3-4に示すように、 $I_C=100A$ 条件において、TO-247では $R_G=20\Omega$ のとき、 $V_{CE(\text{peak})} \approx 810V$ となります。しかし、TO-247-4で同等の $V_{CE(\text{peak})}$ に抑えるには $R_G \approx 51\Omega$ を選定する必要があります。また、 $R_G$ を大きくすると損失が大きくなるため、TO-247-4の特長である低損失を最大限に発揮できなくなります。

そのため、TO-247とTO-247-4の周辺回路はそれぞれの製品において適切な定数の部品選定を行い、サージ電圧が最大定格を超えないように適切なマージンを設けた回路設計をしてください。

図3-4 ターンオフサージ電圧比較

図3-5に示すレイアウトのプリント基板設計することでTO-247とTO-247-4の製品間で互換性を持つことができます。この設計により、製品の置き換えが容易になることや、2種類のパッケージを1つのプリント基板で実装することができます。ただし、周辺の回路定数は製品ごとに適した設定をするようにしてください。

図3-5 プリント基板設計例

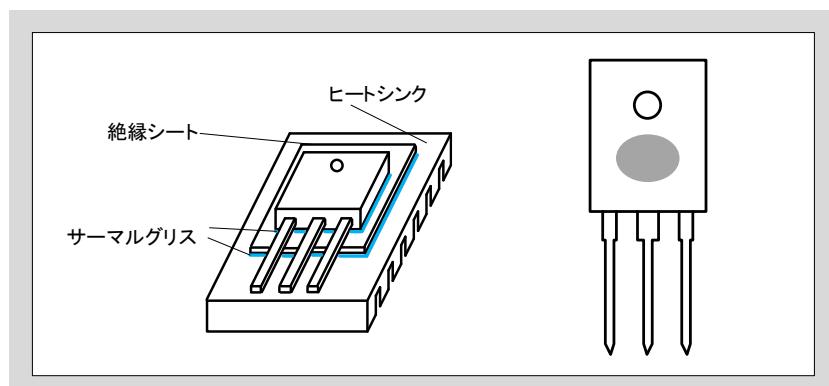

## 10. 実装上の注意事項

ディスクリートIGBTをヒートシンクに取り付ける際には、製品本体とヒートシンクの間の熱伝導を良くし、放熱効果をあげるためサーマルグリスを均一に薄く塗布することを推奨します。サーマルグリス塗布量の不足、不適切な塗布方法により、サーマルグリスが十分に素子全体に広がらず、放熱悪化による熱破壊に繋がる事があります。

サーマルグリスの種類・塗布方法によっては、高温動作時や温度サイクルでサーマルグリスの劣化や枯渇が発生し、製品寿命が低下する可能性があります。サーマルグリスの選定と塗布方法には十分留意して使用してください。

取付け用ネジの締付トルクが小さすぎると熱抵抗が増大し、熱破壊する危険性があります。表3-2の範囲内の数値を推奨します。

表3-2 半導体素子の締付トルク

| パッケージ外形  | 取付穴径 | 使用ネジ | 締付トルク<br>(N・cm) |

|----------|------|------|-----------------|

| TO-247   | φ3.2 | M3   | 40-60           |

| TO-247-4 |      |      |                 |

素子と絶縁シート、絶縁シートとヒートシンク間をサーマルグリスで満たすため、図3-6のように半導体素子チップ搭載部直下のケース部およびヒートシンクの表面へ点状に塗り、推奨締付トルクでヒートシンクにネジで締付けをしてください。また、ヒートシンク面は下記の条件を満たすように仕上げを行ってください。

図3-6 サーマルグリス塗布

- ・ディスクリートIGBTと接触する範囲内のヒートシンク面平坦度  $\leq \pm 30\mu\text{m}$

- ・ディスクリートIGBTと接触する範囲内のヒートシンク表面粗さ  $\pm 10\mu\text{m}$

- ・ねじ穴のテーパー加工は行わないでください。

## 11. はんだ付け

はんだ付け実装時には、通常最大定格の保存温度を超える熱(温度)が端子部に加わります。下記に注意してはんだ付けを行ってください。

表3-3 推奨実装条件

| パッケージ    | 実装方法            |                  |         |        |             |

|----------|-----------------|------------------|---------|--------|-------------|

|          | フローはんだ<br>(全浸漬) | フローはんだ<br>(端子浸漬) | 赤外線リフロー | 温風リフロー | はんだごて       |

| TO-247   | 実装不可            | 二回のみ<br>実装可      | 実装不可    | 実装不可   | 一回のみ<br>実装可 |

| TO-247-4 |                 |                  |         |        |             |

| はんだ温度 / Soldering temp. | 浸漬時間 / Immersion time |

|-------------------------|-----------------------|

| 260±5°C                 | 10±1 sec              |

| 350±10°C                | 3.5±0.5 sec           |

- ・端子の浸漬深さは、デバイス本体から1.5mm離れた位置までにしてください。

- ・フローはんだ方式による製品の取付けなどでは、デバイス本体をはんだに浸さないようにしてください。

- ・フラックスを使用する場合には、塩素系のものを避け、ロジン系のフラックスの使用が望ましいです。

## 12. 洗浄

フラックスを使用してはんだ付けをし、フラックスを洗浄する場合は以下のことに注意してください。

### 12.1 溶剤

- ・引火性・毒性および腐食性のない溶剤を使用してください。

- ・特にトリクロレン系は塩素を含んでいるため使用を避けてください。

### 12.2 洗浄方法

洗浄は浸漬を推奨します。超音波洗浄を行う場合、ディスクリートIGBTやプリント基板が振動源に直接触れないように注意してください。

## 13. 端子の加工、取り付け

### 13.1 端子へのストレス

ディスクリートIGBTの端子は、JEITA規格のED4701/400A試験方法401Aに準拠した信頼性試験を行っています。表3-4に試験内容を示します。試験方法の詳細は、JEITA規格をご確認ください。

下記の試験項目は、未実装のディスクリートIGBTのみに適用されます。実装済みのディスクリートIGBTは、保証の範囲外となりますのでご注意ください。

表3-4 試験内容

| 試験項目  | 試験方法と条件                      | 参照項目                                | サンプル数 |

|-------|------------------------------|-------------------------------------|-------|

| 引張り試験 | 引張り力：2.2 ± 0.1 N<br>保持時間：30秒 | JEITA ED4701/400A<br>試験方法401A 方法I   | 15    |

| 曲げ試験  | 曲げ角度：15度<br>曲げ回数：1回          | JEITA ED4701/400A<br>試験方法401A 方法III | 15    |

| 疲労試験  | 曲げ角度：15度<br>曲げ回数：3回          | JEITA ED4701/400A<br>試験方法401A 方法V   | 15    |

### 13.2 端子成形上の注意点

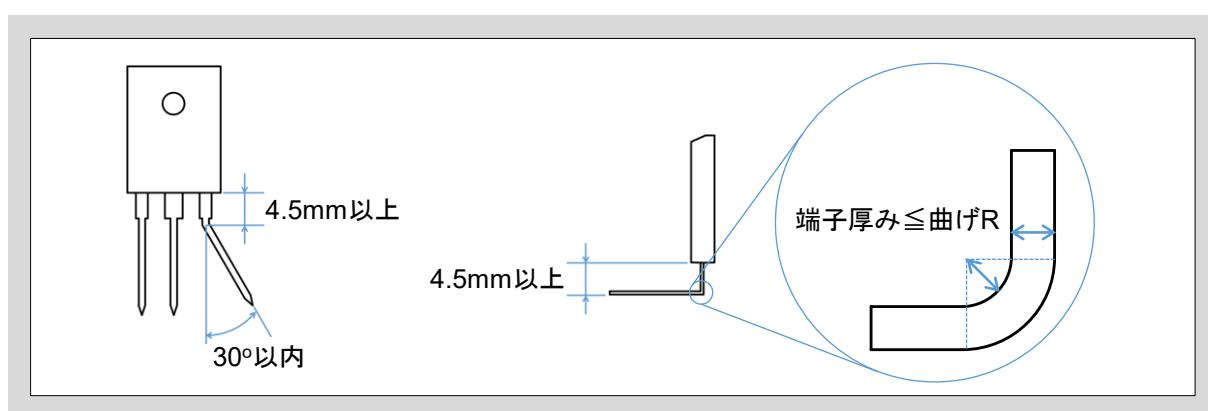

部品配置の都合上やむなく端子を成形する場合は次の注意が必要です。

- ・内部のチップおよび外部パッケージにストレスが加わらない専用の治具を使用してください。

- ・端子を横方向に曲げる場合は、図3-7のようにパッケージから4.5mm以上離れた部分で30°を超えないように折り曲げてください。

- ・端子をパッケージに対し直角に曲げる時は、パッケージから4.5mm以上離れた点で折り曲げてください。

- ・端子を曲げる時の曲げRは、端子厚み以上の曲げRを付けてください。

- ・同一の場所の成形は1回のみとし、再成形や元の形に戻しての使用はしないでください。

図3-7 端子成形上の注意点

### 13.3 プリント基板への挿入

プリント基板に差し込む時は、端子の根元部分に過大なストレスがかからない様に端子の間隔と差し込む穴の間隔を一致させてください。

## 14. 保管

- ・素子の保管温度・湿度は常温・常湿中が好ましく極端な温度・湿度は避けてください。常温常湿の目安は、5~35°Cで45~75%です。非常に乾燥する環境下では、加湿器により加湿する必要があります。その際、水道水を使うと含まれている塩素により製品の端子が錆びる可能性があるので、使用する水は純水や沸騰水を用いるようにしてください。

- ・腐食性ガスを発生する場所や塵埃の多いところは避けてください。

- ・急激な温度変化のある所ではデバイスに結露が起こるので、できるだけ温度変化の少ない場所に保管してください。

- ・保管時における外装箱の積み重ねは5箱までとし、箱の荷崩れや変形を起こさないような処置をしてください。また、重いものを上に載せることも避けてください。

- ・錆などによるはんだ付不良を避けるため各端子は未加工の状態で保管してください。

- ・製品を入れる容器は静電気を帯びにくいもの、あるいは弊社出荷時の容器としてください。

- ・保管棚等は全て金属にし、接地してください。

- ・保管期限は上記の点を保管梱包状態を遵守した状態にて、納入後1年間です。

## 15. 運搬

- ・落下などの衝撃を与えないでください。

- ・多数の製品を箱等で運搬する時は、接触電極面等を傷つけないようにやわらかいスペーサを介して製品を並べてください。

- ・G-E間に静電気が加わらない様に導通性袋やアルミ箔等で静電気対策を行い運搬してください。

図3-8 導電性袋

図3-9 導電性フォーム

## 16. 使用上の注意事項

- 動作中あるいは通電中、製品の端子やパッケージなどに直接手を触れないでください。直接手を触れますと感電や火傷の恐れがあります。

- 万一、不慮の事故で素子が破壊した場合を考慮して、適切な容量のヒューズ、ブレーカなどを必ず付けて2次破壊(火災、爆発など)を防いでください。

- 製品は動作中高温になります。また、製品の封止樹脂には難燃材を使用しておりますが、製品が故障した際、発煙や発火することがあります。発火性のある環境(可燃性ガスが漏洩、蓄積する可能性のある環境など)や可燃物のある場所でご使用される場合は、必ずお客様の責任において延焼防止などの手段を講じてください。

- パッケージ温度、チャネル温度およびリード温度上昇について検討を行ってください。

- 酸、有機物、腐食性ガス(硫化水素、亜硫酸ガスなど)を含む環境下では、製品が酸化や腐食を生じ故障の原因となりますのでご使用は避けてください。

- 耐放射線設計を行っておりませんので、放射線を受けるような環境でのご使用は避けてください。

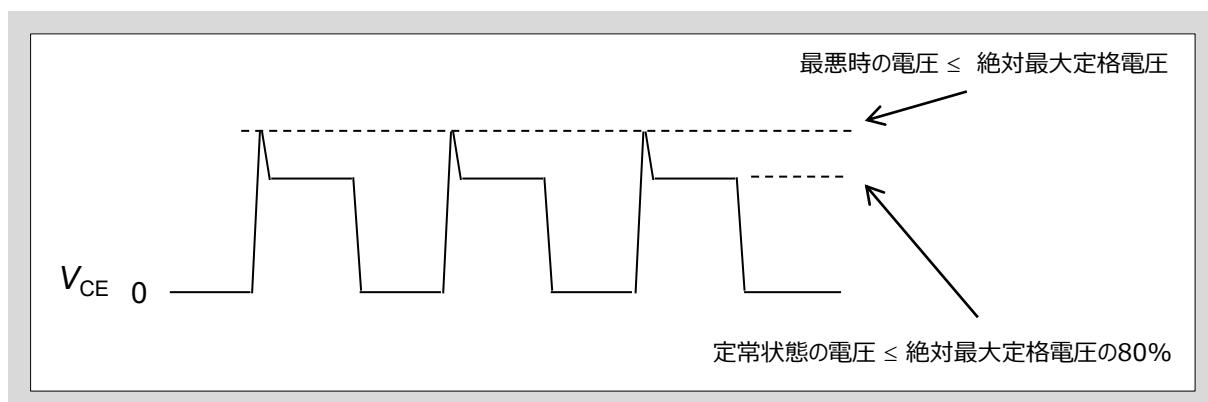

- 図3-10に示すように、定常状態の電圧が絶対最大定格電圧の80%以下で設計・ご使用ください。サージを含めた最悪時の電圧が絶対最大定格以内で設計・ご使用ください。

図3-10 スイッチング時の電圧波形

## 第4章 トラブル発生時の対処方法

|                  |     |

|------------------|-----|

| 1. トラブル発生時の対処方法  | 4-2 |

| 2. 故障判定方法        | 4-7 |

| 3. 代表的なトラブルと対処方法 | 4-9 |

本章ではディスクリートIGBTを取り扱う際のトラブルの対処方法について説明します。

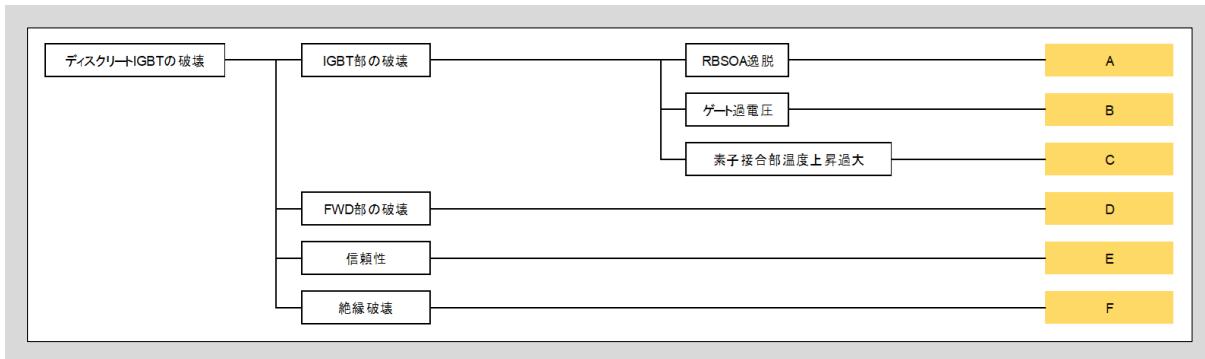

## 1. トラブル発生時の対処方法

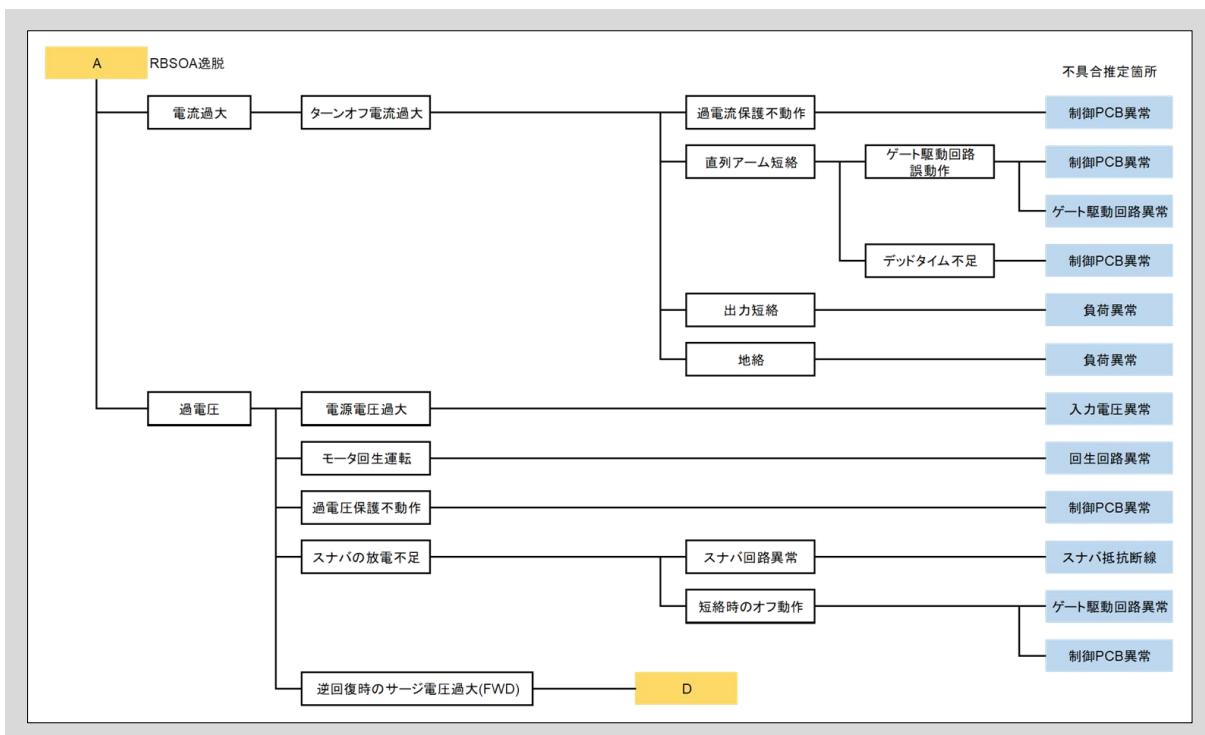

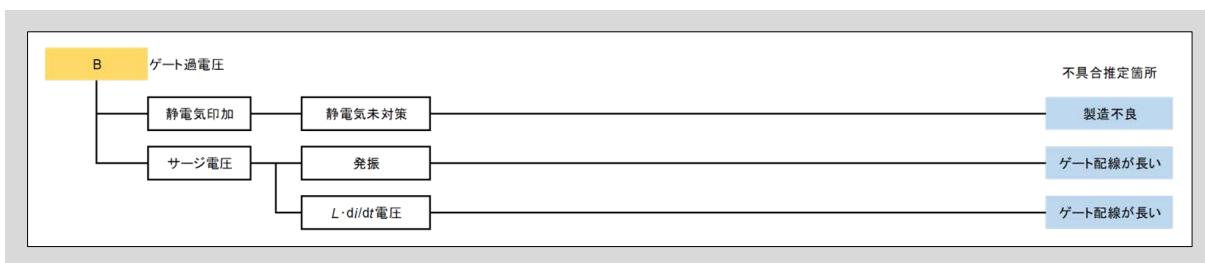

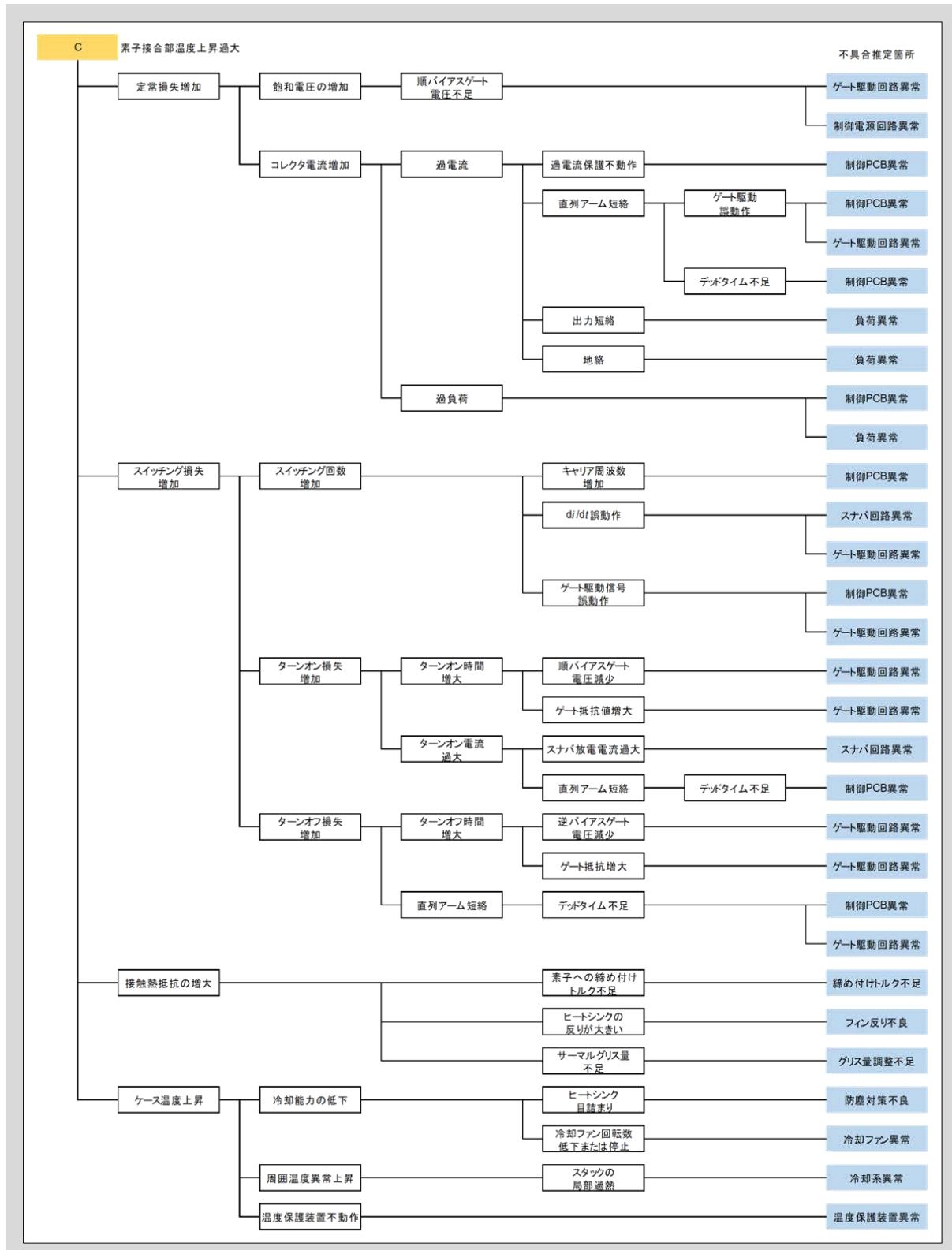

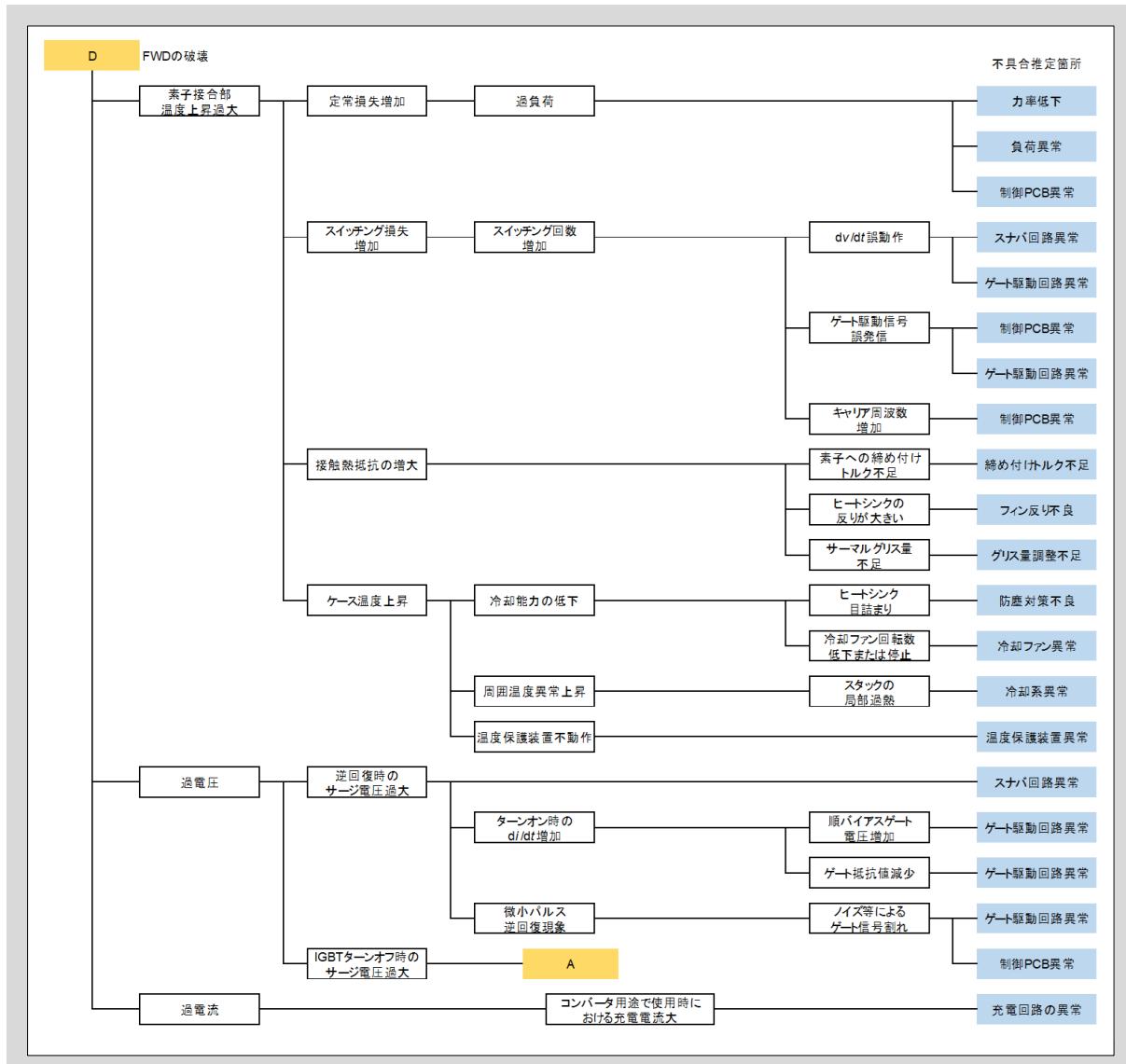

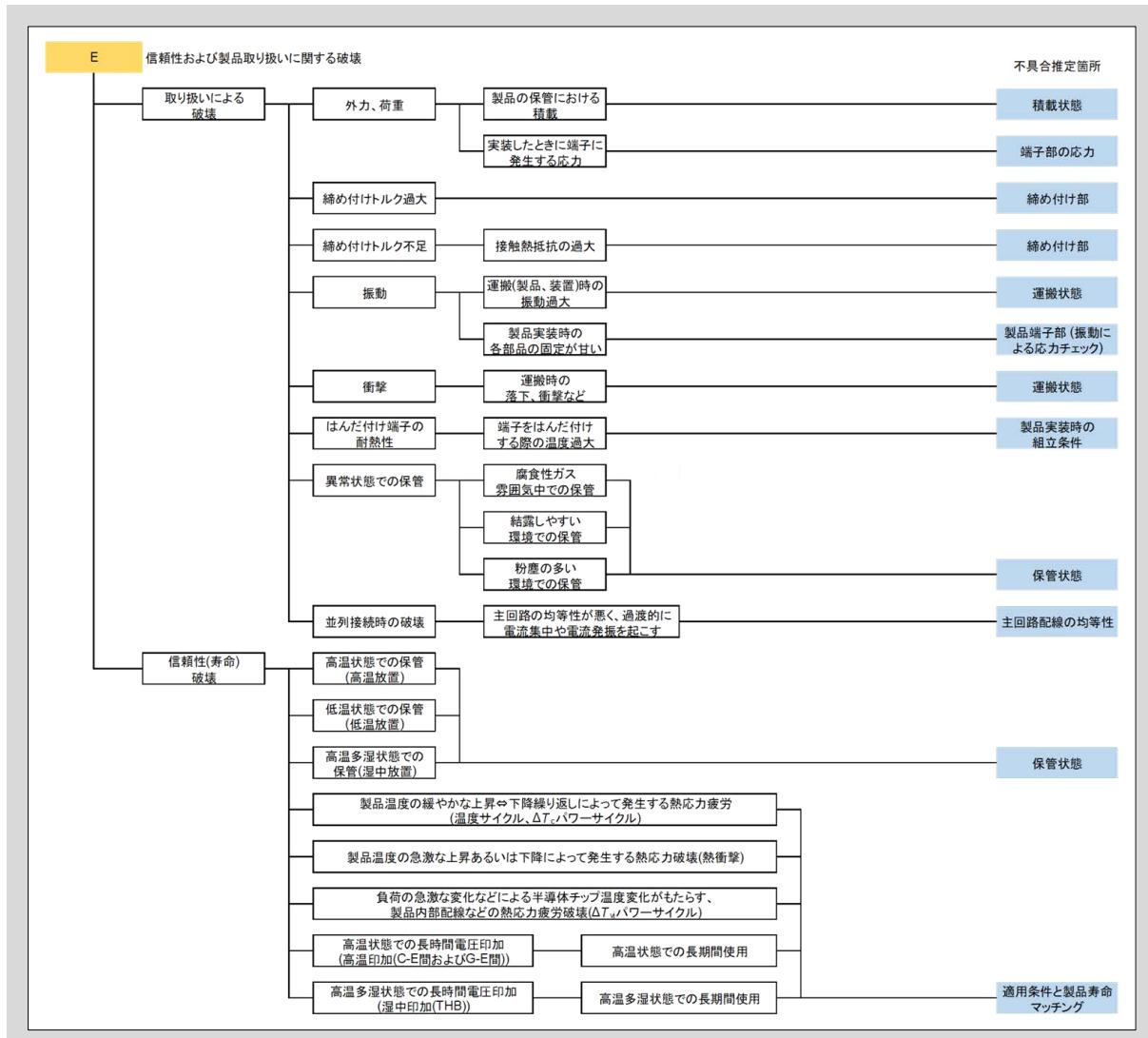

ディスクリートIGBTをインバータ回路などに適用した場合、配線ミス・実装上のミスなどの異常により素子の破壊を招くことがあります。また素子破壊などの異常が発生した場合、発生状況や原因を明確にした上で対策する必要があります。その手引きとして表4-1に素子破壊モードから素子外部の異常現象を推定するための要因解析表を示します。素子が破壊する場合、まずこの表から破壊要因の調査してください。表4-1を用いて原因が解析できない場合、図4-1の詳細な要因解析図を活用して破壊要因を調査してください。また、素子が破壊しているかの確認を行う故障判定方法を本章2項に、代表的なトラブルとその対処方法を本章3項に記載しましたのでこちらも参考にしてください。

表4-1 素子の破壊モードと原因の推定

| 素子外部の異常現象                 |                      | 原 因                                                                                        |                                                    | 素子破壊モード          | チェックポイント                                           |  |

|---------------------------|----------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|----------------------------------------------------|--|

| 短絡                        | 直列アーム短絡<br>(上下アーム短絡) | デッドタイム不足による破壊                                                                              | デッドタイム設定ミス                                         | 過熱(短絡耐量)<br>破壊   | 素子の $t_{off}$ とデットタイムのマッチング                        |  |

|                           |                      | $dv/dt$ 誤動作を起こして短絡破壊                                                                       | ゲート配線が長い                                           |                  | $dv/dt$ 誤ONチェック                                    |  |

|                           |                      | ノイズなどが原因で短絡破壊                                                                              | ゲート駆動回路誤動作<br>ロジック回路誤動作                            |                  | 回路誤動作チェック                                          |  |

|                           | 出力短絡                 | 配線ミス、配線誤接触、負荷短絡                                                                            |                                                    |                  | 不具合発生状況チェック<br>素子耐量と保護回路のマッチング                     |  |

|                           | 地 線                  | 配線ミス、配線誤接触                                                                                 |                                                    |                  | 配線状態チェック                                           |  |

| 過負荷(過電流)                  |                      | 過電流が流れ破壊                                                                                   | ロジック回路誤動作<br>過電流保護設定ミス                             | 過熱               | ロジック回路チェック<br>過電流保護設定値の見直し                         |  |

| 過電圧                       | 直流電圧過大               | C-E間に素子耐圧を超える過電圧が印加され破壊                                                                    | 入力電圧过大<br>過電圧保護                                    | C-E間耐圧<br>オーバー   | 過電圧保護レベル見直し                                        |  |

|                           |                      | ターンオフ時のサージ電圧がRBSOAを超えて破壊                                                                   |                                                    | RBSOA            | ターンオフ動作軌跡とRBSOAのマッチング<br>スナバ回路の見直し                 |  |

|                           |                      | FWD逆回復時のサージ電圧が素子耐圧を超えて破壊                                                                   |                                                    | C-E間耐圧<br>オーバー   | サージ電圧と素子耐量のマッチング<br>スナバ回路の見直し                      |  |

|                           | サージ電圧過大              | ゲート信号がパルス割れなどで非常に短い時間間隔のターンオフターンオン(数百nsオーダー)を起こし、素子耐圧を超える過大な逆回復サージ電圧が発生して破壊(以下、微小パルス逆回復現象) | ノイズによるロジックまたはゲート駆動回路誤動作<br>主回路などからのゲート信号線への電磁誘導    |                  | ロジックおよびゲート信号チェック<br>大電流動作時のゲート信号／信号線の燃線／主回路～信号線の距離 |  |

| 駆動電源電圧減                   |                      | G-E間電圧 $V_{GE}$ が設計値より低下してC-E間電圧 $V_{CE}$ 間電圧が大きくなり、発熱(損失)が大きくなつて破壊                        | DC - DCコンバータ誤動作<br>駆動電源確立迄の時定数が大きすぎる<br>ゲート信号配線はずれ | 過熱               | 回路チェック                                             |  |

| ゲート過電圧                    |                      | 静電気がG-E間に印加されゲートが破壊<br>ゲート配線が長すぎてG-E間に耐圧を超えるサージ電圧が発生し、破壊                                   |                                                    | G-E間耐圧<br>オーバー   | 作業状態チェック(静電気対策)<br>ゲート電圧チェック                       |  |

| ゲートオープンでの駆動               |                      | 受入試験などでゲートオープンの状態でC-E間に電圧を印加(オン電圧／耐圧測定など)して破壊                                              |                                                    | 過熱破壊             | ゲート電圧チェック                                          |  |

| 過熱                        | 放熱能力不足               | 放熱能力不足で素子が異常過熱、最大接合部温度を超えて破壊                                                               | 端子取付けネジのゆるみ<br>サーマルグリスの塗布不足<br>冷却ファン停止             | 過熱               | 放熱条件チェック                                           |  |

|                           |                      | 発生損失増大                                                                                     | ロジック回路誤動作により、キャリア周波数の増加などが起こり、総合損失が上昇して破壊          |                  | ロジック回路チェック                                         |  |

| 応力                        | 応力                   | ディスクリートIGBTの端子部が応力疲労を起こし断線する。                                                              | 外部配線から端子に掛かる応力                                     | 製品内の電気配線断線(オープン) | 端子部に発生する応力／製品および他の部品の実装状態                          |  |

|                           | 振動                   |                                                                                            | 実装した他の部品などが振動して端子に応力を与える                           |                  |                                                    |  |

| 素子の適用条件と信頼性実力のマッチングが取れてない |                      | 素子の適用条件(環境、温度変化、実装時の組立条件、保管状態など)と製品の信頼性実力のマッチングが取れてなく、製品内部の配線、絶縁構造、外観などが破壊                 |                                                    | 破壊モードは場合によって異なる  | 本章図4-1に基づいてチェックしてください                              |  |

図4-1(a) ディスクリートIGBT故障解析図 (※A~D記号は下図へ連結しています)

図4-1(b) モードA:RBSOA逸脱

図4-1(c) モードB:ゲート過電圧

図4-1(d) モードC:素子接合部温度上昇過大

図4-1(e) モードD:FWDの破壊

図4-1(f) モードE:信頼性および、製品取り扱いに関する破壊

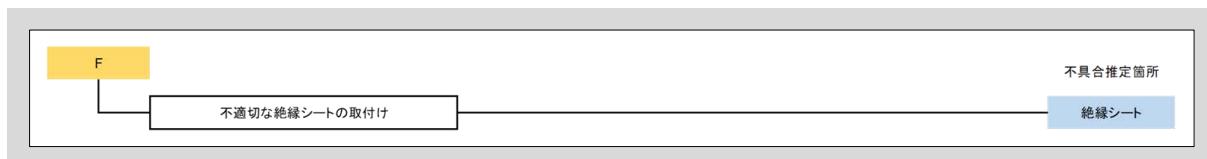

図4-1(g) モードF:絶縁破壊

## 2. 故障判定方法

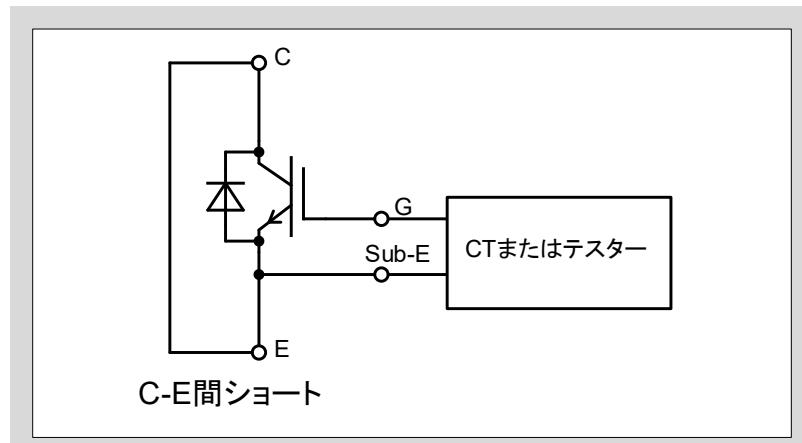

ディスクリートIGBTの故障有無は、トランジスタ特性測定装置(トランジスタ・カーブトレーサ(以下CT))により、次の項目をチェックする事によって判定できます。

- G-E間漏れ電流

- C-E間漏れ電流 (G-E間を必ずショートさせてください)

CTの代わりにテスターなどの電圧、抵抗が測定できる装置を使用しても簡易的に故障判定ができます。

### 2.1 G-E間漏れ電流チェック

図4-2に示す様に、C-E間をショートし、G-E間の漏れ電流あるいは抵抗値を測定します(G-E間には±20Vを超える電圧は印加しないでください。テスターを使用する場合、内部バッテリー電圧が20V以下であることを確認してください)。

製品が正常であれば、仕様書記載の $I_{GES}$ 最大値以下の漏れ電流になります(テスターを使用する場合、抵抗値は数十MΩ～無限大)。それ以外の状況では素子が破壊している可能性があります(一般的に素子が破壊しているとG-E間はショートの状態になります)。

図4-2 G-E間 (ゲート) チェック

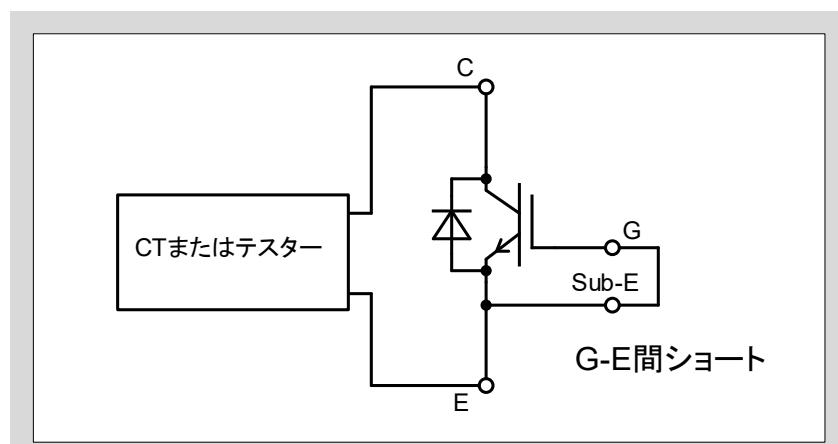

## 2.2 C-E間漏れ電流チェック

図4-3に示すように、G-E間をショートし、C-E間の漏れ電流または抵抗値を測定します。(コレクタを+、エミッタを-に接続します。極性を逆に接続した場合、FWDが導通してC-E間ショートになります。) このとき、C-E間に仕様書記載の $V_{CE}$ を超える電圧は絶対に印加しないでください。

製品が正常であれば、仕様書記載の $I_{CES}$ 最大値以下の漏れ電流になります(テスターを使用する場合、抵抗値は数十MΩ～無限大)。それ以外では素子が破壊している可能性があります(一般的に素子が破壊しているとC-E間はショートの状態になります)。

### ※ 注意

C-G間の耐圧測定は絶対に実施しないでください。耐圧測定した場合、酸化膜に過剰な電圧が加わり絶縁破壊に至ります。

図4-3 C-E間チェック

### 3. 代表的なトラブルと対処方法

#### 3.1 G-E間オープン状態での主回路電圧印加

G-E間オープン状態で主回路電圧印加すると、IGBTの帰還容量 $C_{res}$ を介して電流が流れるためG-E間容量に電荷が充電されゲート電位が上昇します。これによりIGBTがオンして大きなコレクタ電流 $I_C$ が流れ素子が破壊します。(第3章4項参照) G-E間はオープン状態にならないよう、10kΩ程度の抵抗挿入などの対策をしてください。

製品の受入試験などの際にも、ロータリースイッチなどの機械スイッチで信号線の切り替えを行うと、切り替え時にG-E間が瞬時オープンになります。C-E間に電圧印加したまま、機械スイッチで信号線の切り替えを行うと、上記の現象で素子が破壊する事が有ります。また機械スイッチがチャタリングする場合も同様な期間が存在し素子破壊します。破壊を防ぐため、必ず主回路(C-E間)電圧を0Vまで放電してからゲート信号の切り替えを行ってください。

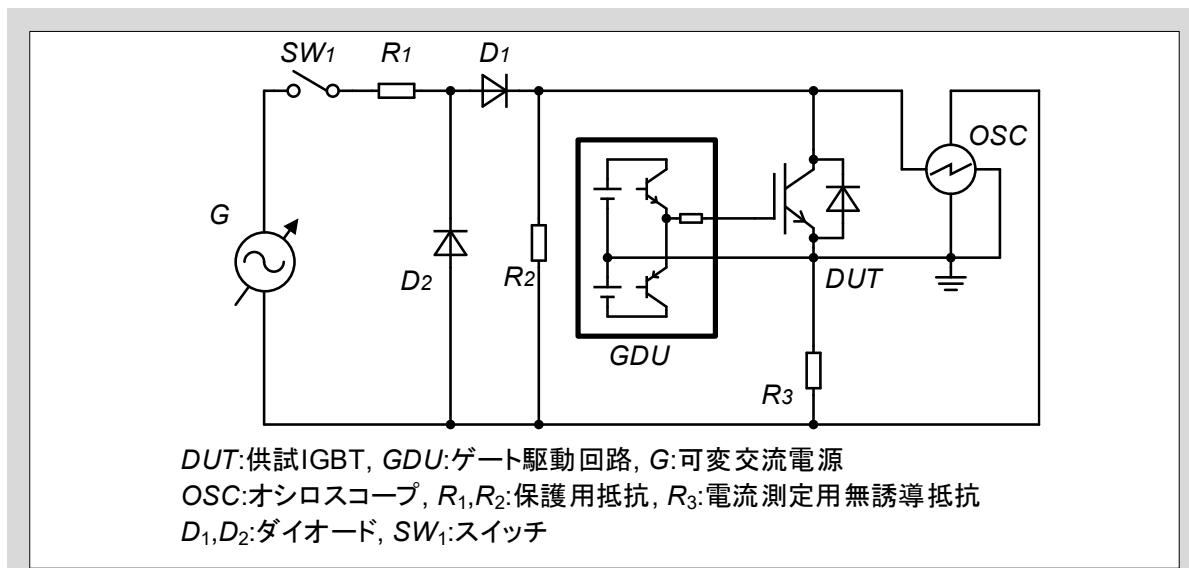

図4-4はオン電圧測定回路の例です。この回路で測定手順を説明します。まずゲート駆動回路(GDU: Gate Drive Unit)をオフ状態( $V_{GE} \leq 0V$ )にしてから $SW_1$ をオンしC-E間に電圧を印加します。次に、GDUよりG-E間に所定の順バイアス電圧を印加してIGBTを通電させ、オン電圧を測定します。最後にゲート回路をオフ状態にして $SW_1$ をオフにします。この様な手順を踏めば製品を破壊する事なく安全に製品の特性を測定する事が出来ます。

図4-4 オン電圧の測定回路

### 3.2 $-V_{GE}$ 不足によるIGBT誤点弧

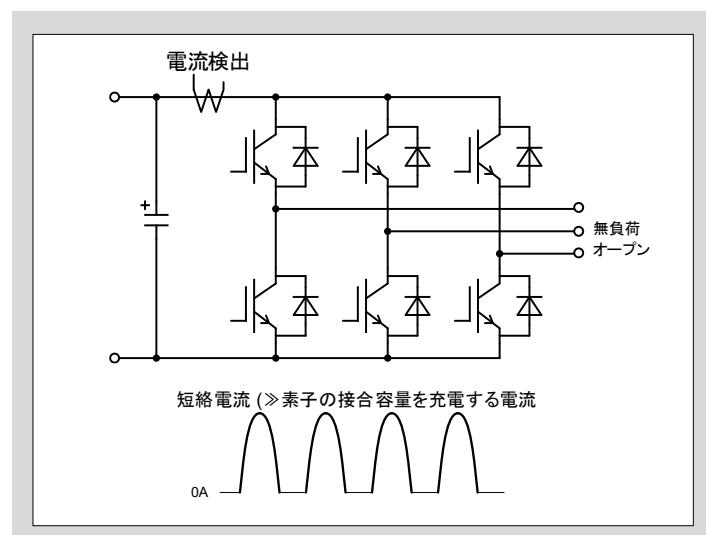

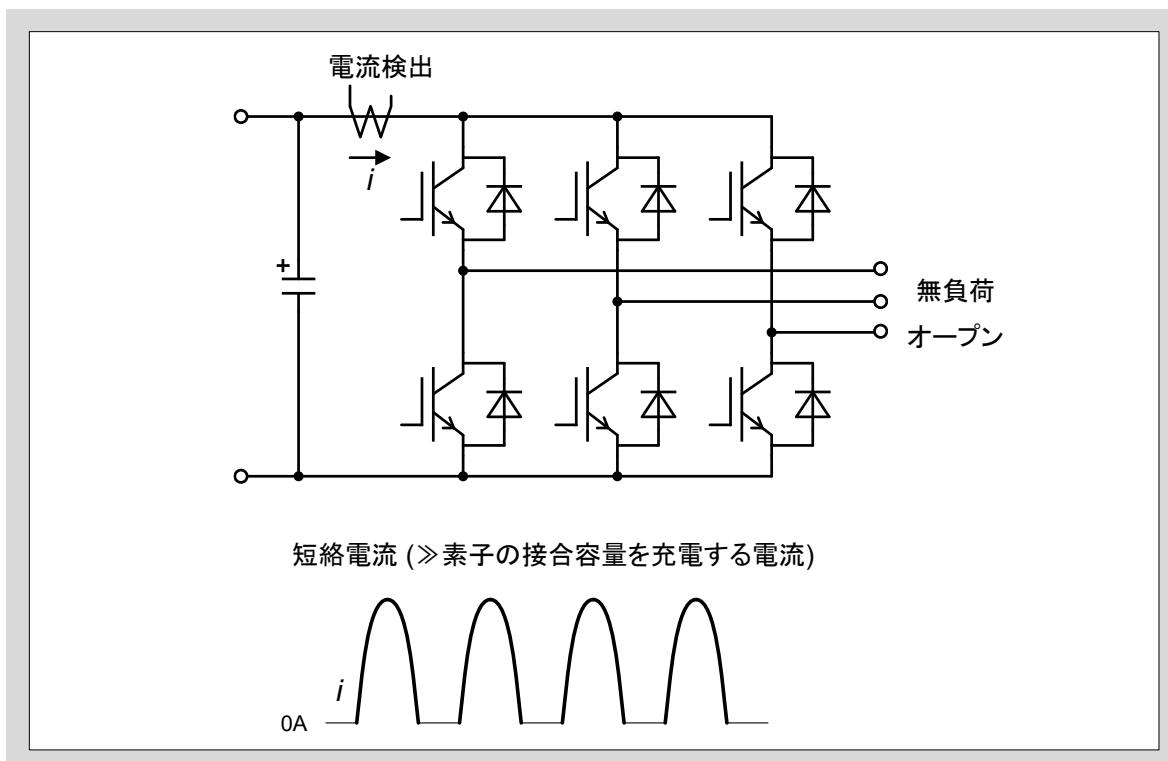

三相インバータのような回路に適用する場合、オフ状態のIGBTが誤点弧すると上下アームIGBTの両方がオンして短絡電流が流れることができます。短絡電流遮断時のサージ電圧や発生損失により製品が破壊する可能性がありますので、装置を設計する際、必ず上下アーム短絡が発生していないことを確認してください。また、 $dv/dt$ 発生による誤動作発生メカニズムの詳細を第7章1.4項に記載していますので参照してください。

IGBTオフ時誤動作による上下アーム短絡電流の有無を確認する方法例を図4-5に示します。まずインバータの出力端子(U、V、W)をオープン(無負荷)にします。次にインバータを起動し各IGBTを駆動します。この時、図の様に電源ラインから流れる電流を検出すれば上下アーム短絡電流有無が確認できます。もし、誤動作が無ければ、素子の接合容量を充電する非常に微小なパルス電流(定格電流の5%程度)のみが測定されます。

オフIGBTが誤動作し短絡が発生すると、この電流が大きくなります。正確に測定するためには、逆バイアス( $-V_{GE}$ )の有無でこのパルス電流に差が無ければ誤点弧を起こしていないことになります。上記方法で誤点弧が確認された場合の対策は、短絡電流が無くなる逆バイアス( $-V_{GE}$ )を持つゲート駆動回路にするか、G-E間に仕様書に記載の $C_{ies}$ に対し2倍程度の容量( $C_{GE}$ )をゲート抵抗 $R_G$ よりディスクリートIGBT側へ付加する事を推奨します。

但し、単純に $C_{GE}$ を付加する方法は、スイッチング時間やスイッチング損失が大きくなる場合があります。それらを $C_{GE}$ 付加前と同等とするための一例として $R_G$ を $C_{GE}$ 付加前に対して概ね半分へ変更することを推奨します。この状態において適用可否の検討を再度十分に行ってください。

なお、上下アームに短絡電流が流れる要因は上記の $dv/dt$ 誤点弧以外にもデッドタイム不足があります。この現象が起きている時にも図4-5に示す試験で短絡電流が観測されますので、 $-V_{GE}$ を増加しても短絡電流が減少しない場合、デッドタイムを増加するなどの対策を施してください。デッドタイムに関しては第7章3項に詳しい説明がありますので参照してください。

図4-5 短絡電流の測定回路

### 3.3 過渡オン状態からのダイオード逆回復(微小パルス逆回復)現象

ディスクリートIGBTにはFWDを内蔵している製品があります。このFWDの挙動に十分な注意を払うことは信頼性の高い装置を設計するためには非常に重要です。この項では特に微小パルス逆回復現象という製品破壊につながりやすい現象について説明します。

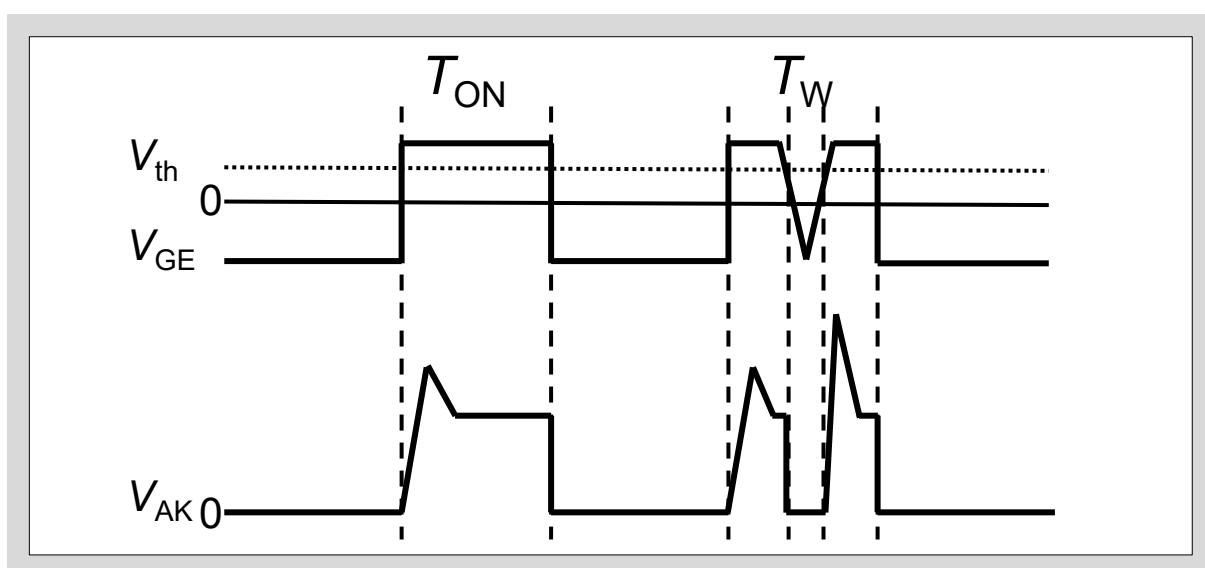

微小パルス逆回復現象はIGBT駆動時にノイズなどによってゲート信号割れが起き、非常に過大な逆回復サージ電圧が発生する現象です。図4-6に微小パルス逆回復による過大サージ電圧の発生タイミングチャートを示します。 $V_{GE}$ のオン期間 $T_{ON}$ に対して非常に短いオフパルス $T_W$ が発生した場合、対向アーム側のFWDはオンしてから非常に短い時間で逆回復に入ることになります。本来の逆回復では十分なキャリアを蓄積してから逆回復に入るのに対して、微小パルス逆回復ではFWDに十分なキャリアの蓄積がない状態で逆回復することになります。これによりFWDの空乏層が急激なスピードで拡がるため、急峻な $di/dt$ 、 $dv/dt$ が発生します。これが原因となってC-E(K-A)間に、非常に過大な逆回復サージ電圧が発生します。この現象によって製品の耐圧保証値を超えるサージ電圧が発生すると素子破壊に繋がる可能性があります。

図4-6 微小パルス逆回復による過大サージ電圧の発生

装置設計を行う際には、最小 $T_W$ におけるサージ電圧が素子耐圧以下になることを確認してください。もしサージ電圧が素子耐圧を超える時は以下に記載のサージ電圧対策を実施してください。

- $R_G$ を大きくする

- 回路インダクタンスを低減する

- スナバ回路を強化する

- $C_{GE}$ を付加する

- アクティブクランプ回路を付加する

### 3.4 EMCノイズ対策

電力変換装置は欧州のCEマーキングや国内のVCCI規格への対応が要求されることがあり、EMIノイズ(装置が運転時に発生する伝導性および放射性のノイズ)を規格値以下に抑制することが装置の設計において重要な課題となっています。

ディスクリートIGBTは特性改良による高速スイッチング化・低損失化が進んできているため、IGBTをスイッチングする際に発生する高い $dV/dt$ 、 $di/dt$ が放射性ノイズの原因となる場合が多くなってきています。放射性ノイズの主な要因は、IGBTがターンオン(対向アーム側のFWDが逆回復)する際に生じる高い $dV/dt$ 、 $di/dt$ がトリガとなって、半導体デバイスの接合容量などと配線上のインダクタンスとで生じる高周波のLC共振によるものと考えられます。

ディスクリートIGBTがスイッチングすることによって発生する放射性ノイズを低減させるためには、駆動条件の見直しによるスイッチング特性、特にターンオン特性をソフト(低速)化することが有効です。第7章を参照し、適切な駆動条件を検討してください。

ただし、スイッチング特性をソフト化して放射性ノイズを抑制すると、スイッチング損失は増加傾向となりますので、装置の運転条件やディスクリートIGBT冷却条件などとのバランスを考慮しながら駆動条件を設定することが重要です。

また放射性ノイズの一般的な対策例を表4-2に示します。放射性ノイズは装置の配線構造や材質・回路構成などによりその発生要因・ノイズレベルが異なるので、それぞれの対策例の有効性は個別に検証が必要です。

表4-2 放射性ノイズ対策例

| 対 策                                  | 内 容                               | 備 考                               |

|--------------------------------------|-----------------------------------|-----------------------------------|

| 駆動条件の見直し<br>( $dV/dt$ 、 $di/dt$ の低減) | $R_G$ (特にターンオン側)を大きくする。           | スイッチング損失が大きくなる。<br>スイッチング時間が長くなる。 |

|                                      | G-E間に小容量のコンデンサを接続する。              | スイッチング損失が大きくなる。<br>スイッチング時間が長くなる。 |

| スナバコンデンサをディスクリートIGBTと最短で接続           | スナバコンデンサとディスクリートIGBTの間の配線を最短にする。  | スイッチング時のサージ電圧や $dV/dt$ 抑制にも効果あり。  |

| 配線インダクタンスの低減                         | 直流バスラインを平行導体化してインダクタンスを低減する。      | 同上                                |

| フィルタ                                 | 装置の入出力にノイズフィルタを挿入する。              | 各種市販品あり                           |

| 配線のシールド                              | 入出力ケーブルをシールドしてケーブル部分の放射性ノイズを低減する。 |                                   |

| 装置ケースの金属化                            | 装置筐体を金属化し、装置から放射されるノイズを抑制する。      |                                   |

## 第5章 保護回路設計方法

|              |     |

|--------------|-----|

| 1. 短絡(過電流)保護 | 5-2 |

| 2. 過電圧保護     | 5-8 |

本章では、ディスクリートIGBTの保護回路設計方法について説明します。

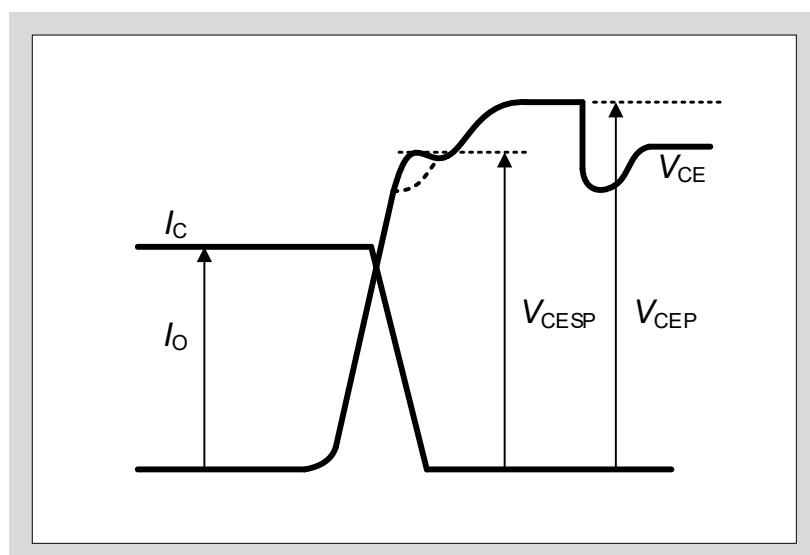

## 1. 短絡(過電流)保護

### 1.1 短絡耐量について

装置が何らかの異常により短絡状態になるとIGBTのコレクタ電流 $I_C$ が増加し、所定の値を超えるとC-E間電圧 $V_{CE}$ が急増します。この特性により、短絡時の $I_C$ を一定の値以下に抑制しますが、IGBTに高電圧・大電流が印加された状態になり、この状態が続くと破壊に至ります。IGBTがこの状態を非破壊で耐え得る時間を短絡耐量と言います。

ディスクリートIGBT XSシリーズでは短絡耐量とトレードオフの関係にある低スイッチング損失と低飽和電圧に特化した設計にしており、短絡耐量の保証をしていません。そのため、短絡が想定される回路には、XSシリーズを使用しないでください。

アーム短絡と出力短絡についての考え方を、以下に説明します。

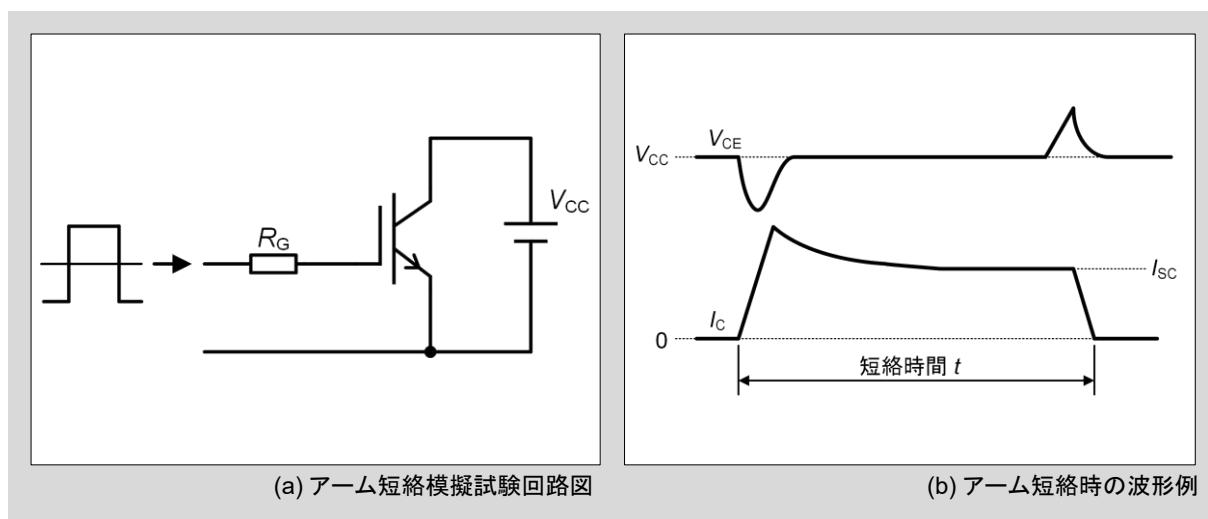

#### 1.1.1 アーム短絡

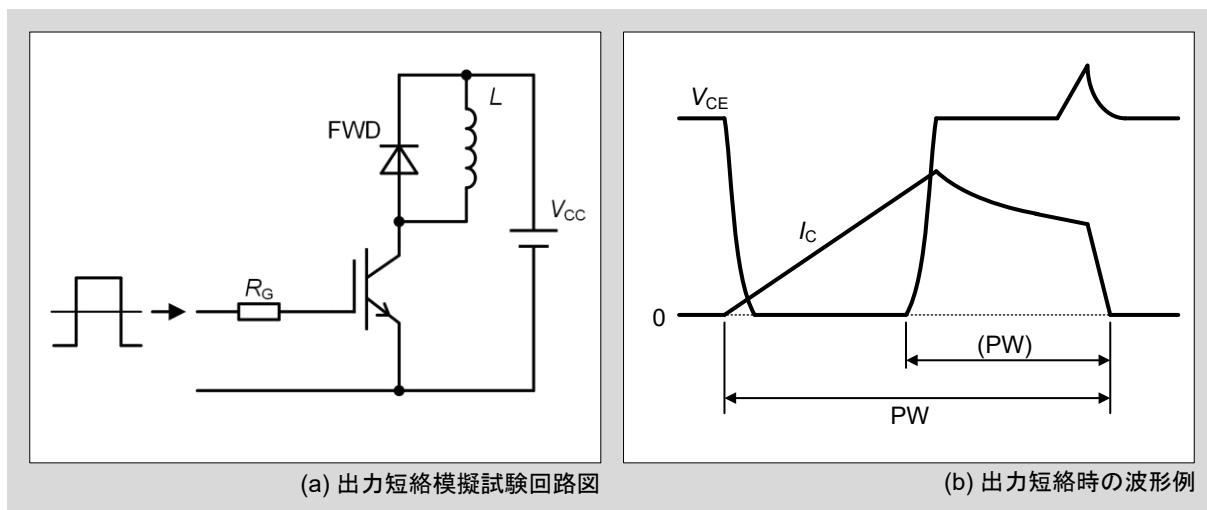

図5-1にアーム短絡模擬試験回路図と波形例を示します。アーム短絡では、短絡開始と共に $I_C$ は急激に上昇し、飽和後に若干低下します。短絡(飽和)電流値 $I_{SC}$ はG-E間電圧 $V_{GE}$ と素子出力特性および接合温度 $T_{vj}$ で決まり、電源電圧 $V_{CC}$ 、ゲート抵抗 $R_G$ 、パルス幅には殆ど依存しません。

図5-1 アーム短絡模擬試験回路および波形

### 1.1.2 出力短絡

図5-2に出力短絡模擬試験回路と波形を示します。出力短絡では短絡線がインダクタンス分を持っているので、短絡開始時の電流波形はアーム短絡の場合と異なります。この場合電流上昇率 $di/dt$ は、

$$di/dt = V_{CC}/L \text{ [A/sec]}$$

で表され、短絡時間を $t$  (sec)とすれば、

$$I_C = di/dt \cdot t \text{ [A]}$$

で計算できます。 $I_C$ 到達値はインダクタンス分や駆動回路( $V_{GE}$ 過渡上昇)などに依存しますが、ピーク値に達し、飽和した後は $V_{CE}$ が上昇しアーム短絡時と同じになります。

電流上昇中、 $V_{CC}$ はインダクタンス $L$ にかかり、IGBTにはC-E間飽和電圧 $V_{CE(sat)}$ 程度の電圧が加わります。このとき、IGBTの負荷はアーム短絡と比べてきわめて低いので、この期間は短絡時間内に含めず考えることができます。

図5-2 出力短絡模擬試験回路および波形

## 1.2 短絡モードと発生原因

三相インバーター装置を例として、短絡モードと発生原因について表5-1に示します。

表5-1 短絡モードと発生原因

| 短絡経路    | 原因                        |

|---------|---------------------------|

| アーム短絡   | IGBTまたはダイオードの破壊           |

| 直列アーム短絡 | 制御回路、駆動回路の故障、またはノイズによる誤動作 |

| 出力短絡    | 配線作業など的人為的なミスおよび負荷の絶縁の破壊  |

| 地絡      | 配線作業など的人為的なミスおよび負荷の絶縁の破壊  |

### 1.3 短絡検出方法

以下に短絡検出方法を説明します。ただし、これら検出方法はVシリーズのみ適用可能です。短絡が想定される回路ではXSシリーズを使用しないでください。

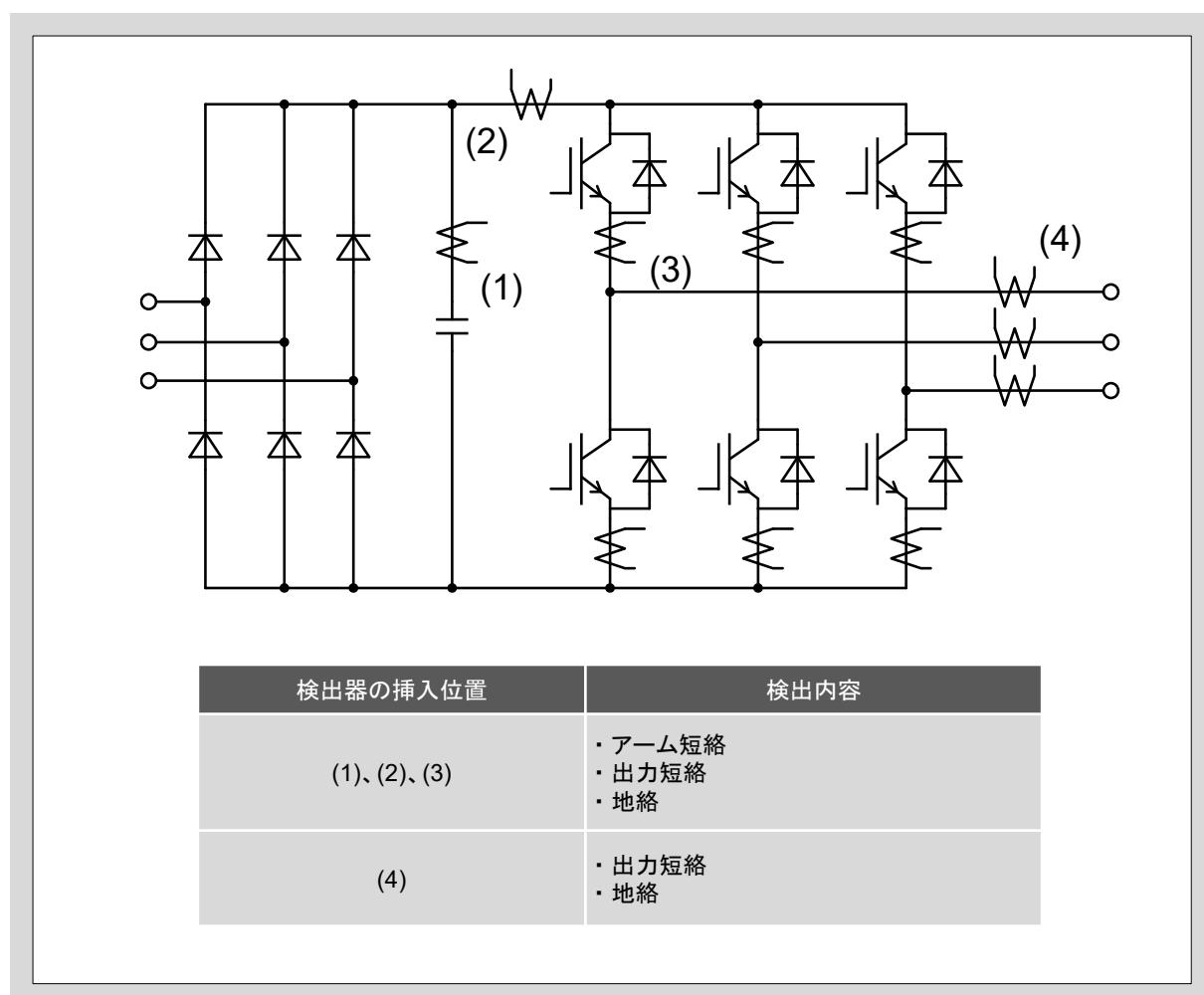

#### 1.3.1 過電流検出器による検出

前述したようにIGBTは短時間での保護が必要となるので、過電流検出からターンオフ完了までの各回路の動作遅れ時間が最小になるように設計してください。

なお、IGBTのターンオフ時間は極めて早いので通常のゲート駆動信号で短絡時の過電流を遮断すると $V_{CE}$ の跳ね上がりが大きくなり、IGBTが過電圧で破壊(RBSOA破壊)する可能性があります。過電流を遮断する際は、IGBTのターンオフをゆるやかにさせること(ソフトターンオフ)を推奨します。

図5-3に過電流検出器の挿入方法を、表5-2にそれぞれの方法の特性と検出可能な内容を示します。どのような保護が必要か検討し、適切な方法を選択してください。

図5-3 過電流検出器の挿入方法

表5-2 過電流検出器の挿入位置と検出内容

| 検出器の挿入位置                  | 特性                                | 検出内容                               |

|---------------------------|-----------------------------------|------------------------------------|

| 平滑コンデンサと直列に挿入<br>図5-3/(1) | ・AC用電流センサ(CT)が使用可能<br>・検出精度が低い    | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| インバータの入力に挿入<br>図5-3/(2)   | ・DC用CTの使用が必要<br>・検出精度が低い          | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| 各素子と直列に挿入<br>図5-3/(3)     | ・DC用CTの使用が必要<br>・検出精度が高い          | ・アーム短絡<br>・直列アーム短絡<br>・出力短絡<br>・地絡 |

| インバータの出力に挿入<br>図5-3/(4)   | ・高周波出力の装置ではAC用CTの使用可能<br>・検出精度が高い | ・出力短絡<br>・地絡                       |

### 1.3.2 $V_{CE(sat)}$ による検出

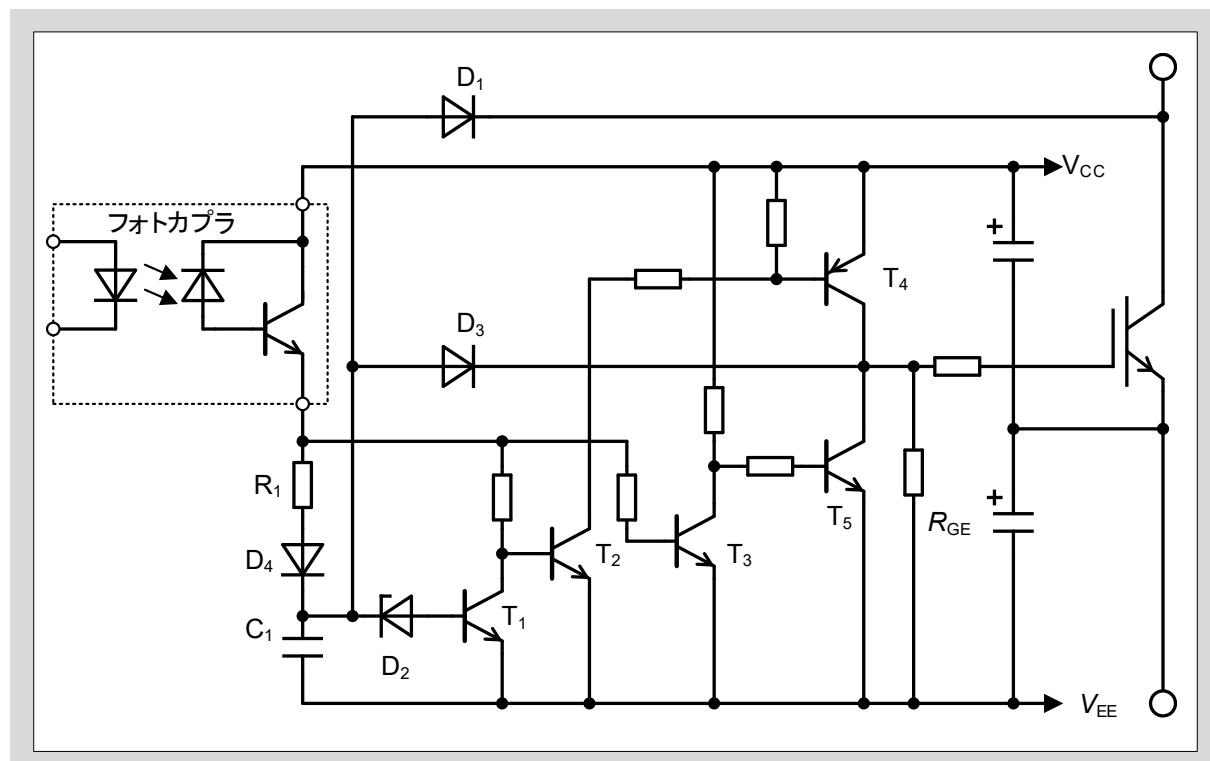

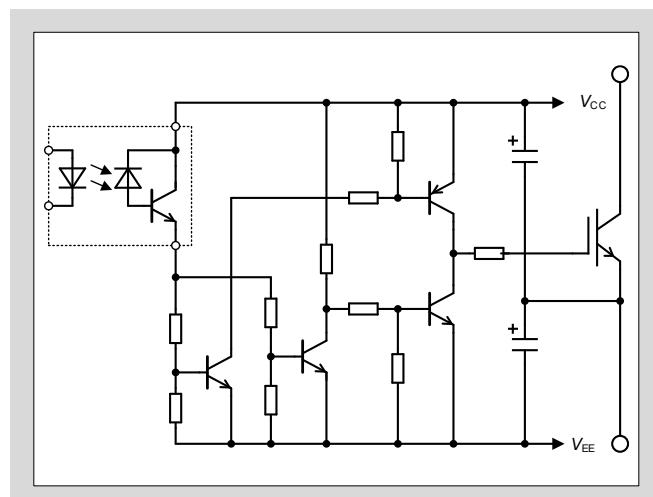

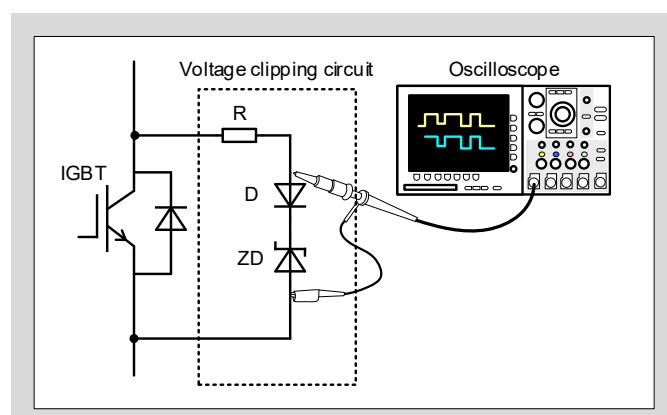

この方法は、表5-1に示す全ての短絡事故に対する保護が可能であり、過電流検出から保護までの動作がゲート駆動回路側で行われるので、最も高速な保護動作が可能となります。図5-4に $V_{CE(sat)}$ 検出による短絡保護回路例を示します。

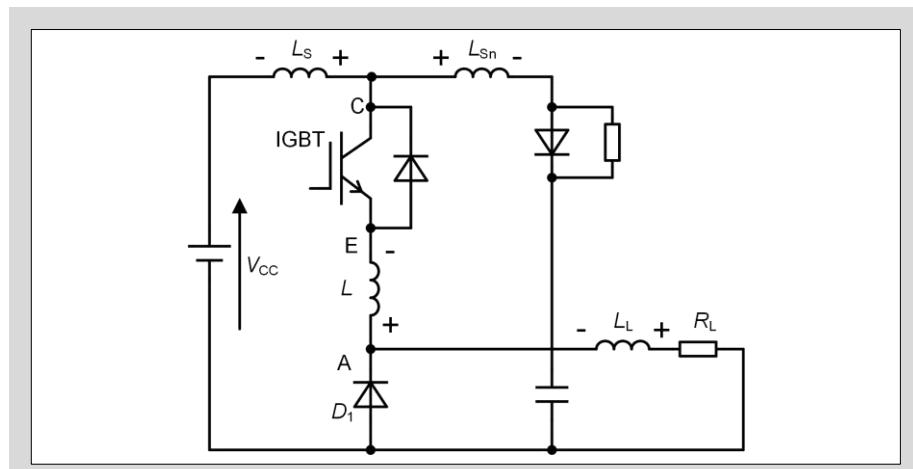

図5-4  $V_{CE(sat)}$ 検出による短絡保護回路例

この回路はIGBTのC-E間電圧をダイオードD<sub>1</sub>を介して監視する回路です。

ターンオン：フォトカプラがオンするとトランジスタT<sub>2</sub>、T<sub>4</sub>がオンしIGBTに+のゲート電圧を印加します。またフォトカプラのオンにより、抵抗R<sub>1</sub>とダイオードD<sub>4</sub>を通してコンデンサC<sub>1</sub>を充電します。このときC<sub>1</sub>の電圧によって、動作が変わります。

【短絡保護動作】

IGBTオン後、短絡状態が発生するとIGBTのV<sub>CE</sub>が上昇します。IGBTのV<sub>CE</sub>が[C<sub>1</sub>の電圧-D<sub>1</sub>の電圧(V<sub>F</sub>-V<sub>EE</sub>)]より高くなると、D<sub>1</sub>がオフとなり、C<sub>1</sub>の電圧が再び上昇します。

C<sub>1</sub>の電圧が[ツエナーダイオードD<sub>2</sub>のV<sub>Z</sub>+トランジスタT<sub>1</sub>のV<sub>BE</sub>]より高くなると短絡保護動作します。

短絡保護動作では、D<sub>2</sub>を通してT<sub>1</sub>のベースに電流が流れT<sub>1</sub>がオンします。T<sub>1</sub>オンによりT<sub>2</sub>、T<sub>4</sub>がオフし、印加していた+のゲート電圧が遮断されます。

フォトカプラはオンしているため、トランジスタT<sub>3</sub>オン、トランジスタT<sub>5</sub>オフ状態を保持しています。T<sub>4</sub>、T<sub>5</sub>が同時オフとなるためゲート蓄積電荷はR<sub>GE</sub>を通してゆっくり放電します。この効果によりIGBTがターンオフする際の過大なサージ電圧の発生を抑制できます。

【通常動作】

IGBTオン後、C<sub>1</sub>の電圧が[D<sub>2</sub>のV<sub>Z</sub>+T<sub>1</sub>のV<sub>BE</sub>]以下の電圧を保持することで、IGBTのオン状態を保持します。

フォトカプラがオフするとT<sub>2</sub>、T<sub>4</sub>オフ、T<sub>3</sub>オフ、T<sub>5</sub>オンとなり、IGBTに-のゲート電圧を印加します。C<sub>1</sub>の電荷はダイオードD<sub>3</sub>、T<sub>5</sub>を通して放電し0Vにリセットします。

上記動作シーケンスからわかるように、短絡保護は各パルスごとで動作します。

## 2. 過電圧保護

### 2.1 過電圧の発生要因と抑制方法

#### 2.1.1 過電圧発生要因

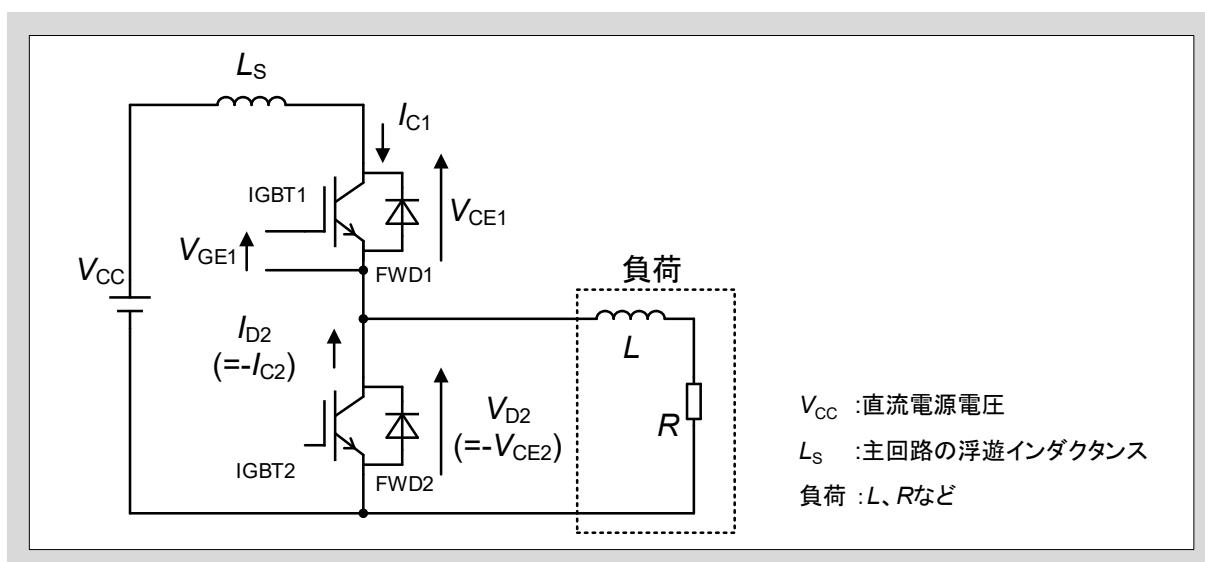

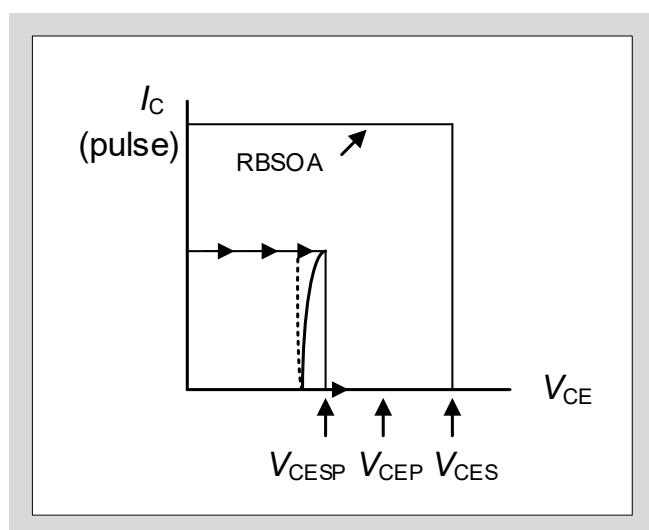

IGBTはスイッチング速度が速いため、IGBTターンオフ時、またはFWD逆回復時に高い $dV/dt$ を発生し、ディスクリートIGBT周辺の配線インダクタンス $L_s$ によるターンオフサージ電圧 $V_{CEP} = L_s \cdot (di/dt)$ が発生します。

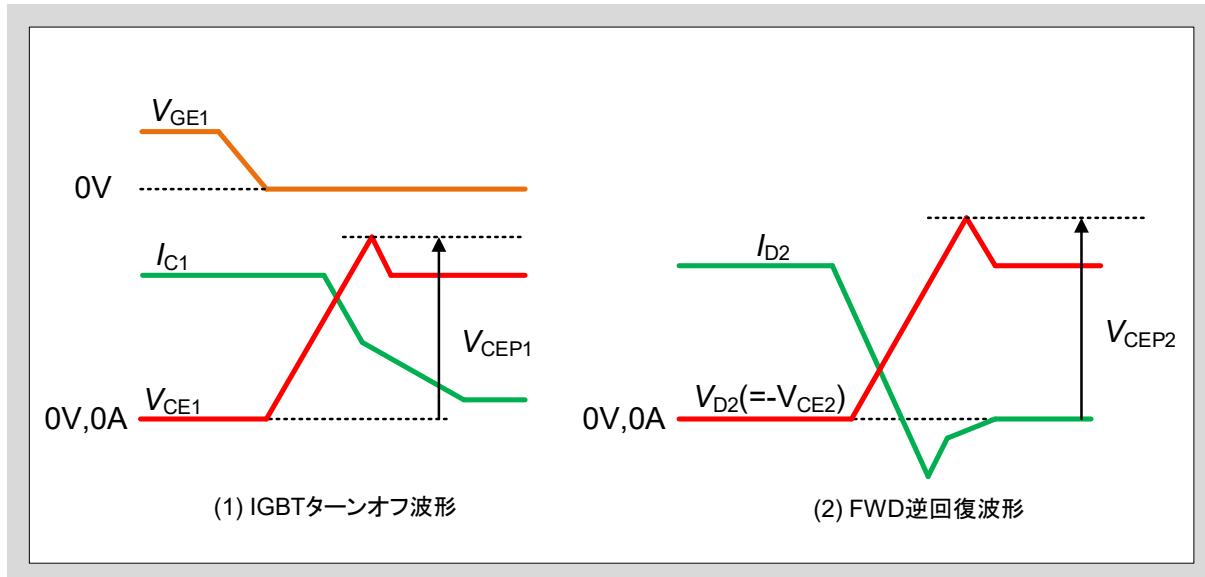

ここではIGBTターンオフ時の電圧・電流波形を例にとって発生要因と抑制方法を紹介し、具体的な回路例(IGBT、FWD共に適用可)を説明します。ターンオフサージ電圧を測定するための簡易的な回路として図5-5に回路例を、図5-6にIGBTのターンオフ波形とFWDの逆回復波形を示します。

図5-5 チョッパ回路

図5-6 動作波形

ターンオフサージ電圧はIGBTがターンオフする際の主回路電流の急激な変化によって、主回路の浮遊 $L_S$ に高い電圧が誘起されることにより発生します。

ターンオフサージ電圧の尖頭値は次式で求められます。

$$V_{CESP} = V_{CC} + \left(-L_S \cdot \frac{dI_C}{dt}\right) \quad dI_C/dt: \text{ターンオフ時のコレクタ電流変化率の最大値}$$

$V_{CESP}$ がIGBTのC-E間耐圧 $V_{CES}$ を超えると破壊に至ることがあります。

### 2.1.2 過電圧抑制方法

過電圧発生要因であるターンオフサージ電圧を抑制する方法として下記の方法があります。

- IGBTにスナバなどの保護回路を付けてサージ電圧を抑制する。スナバ回路のコンデンサにはフィルムコンデンサを用い、ディスクリートIGBTの近くに配置して高周波サージ電圧を抑制させる。

- IGBT駆動回路の $-V_{GE}$ や $R_G$ を調整し $dI/dt$ を小さくする(詳細は第7章を参照してください)。

- 電解コンデンサをできるだけIGBTの近くに配置し、 $L_S$ を低減する。低インピーダンスタイプのコンデンサを用いるとさらに効果的。

- 主回路およびスナバ回路の $L_S$ を低減するために、配線をより太く・短くする。

- ゲート駆動回路にアクティブクランプ回路を適用し、配置したツェナーダイオードの降伏電圧と概ね等しいサージ電圧に抑制する。

## 2.2 スナバ回路の種類と特徴

スナバ回路には全ての素子に1対1で付ける個別スナバ回路と直流母線間に一括で付ける一括スナバ回路があります。

### 2.2.1 個別スナバ回路

個別スナバ回路の代表的な例として、下記のスナバ回路があります。

- RCスナバ回路

- 充放電形RCDスナバ回路

- 放電阻止形RCDスナバ回路

表5-3に各個別スナバ回路の接続図と特性および主な用途を示します。

### 2.2.2 一括スナバ回路

一括スナバ回路の代表的な例として、下記のスナバ回路があります。

- Cスナバ回路

- RCDスナバ回路

最近ではスナバ回路簡素化の目的で一括スナバ回路が使用されることが多くなってきています。

表5-4に各一括スナバ回路の接続図と特性および主な用途を示します。

表5-3 個別スナバ回路の接続図

| スナバ回路接続図                                                                                                    | 特 性(注意事項)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RCスナバ回路</b><br>         | <ul style="list-style-type: none"> <li>一括スナバ回路に比べサージ電圧抑制効果が大きい。</li> <li>大容量のIGBTに適用する際には、スナバ抵抗を低い値にする必要があり、この結果ターンオン時の<math>I_C</math>が増大しIGBTの負担が大きくなる。</li> </ul>                                                                                                                                                                                                                                                                                                     |

| <b>充放電形RCDスナバ回路</b><br>   | <ul style="list-style-type: none"> <li>サージ電圧抑制効果あり。</li> <li>RCスナバ回路と異なり、スナバダイオードが追加されているのでスナバ抵抗値を大きくでき、ターンオン時のIGBTの負担を考えなくてよい。</li> <li>充放電形RCDスナバ回路のスナバ抵抗における発生損失は下式で求められる。</li> </ul> $P = \frac{L_S \cdot I_0^2 \cdot f}{2} + \frac{C_S \cdot V_{CC}^2 \cdot f}{2}$ <p> <math>L_S</math> : 主回路の浮遊インダクタンス<br/> <math>I_0</math> : IGBTのターンオフ時コレクタ電流<br/> <math>C_S</math> : スナバコンデンサ容量<br/> <math>V_{CC}</math> : 直流電源電圧<br/> <math>f</math> : スイッチング周波数         </p> |

| <b>放電阻止形RCDスナバ回路</b><br> | <ul style="list-style-type: none"> <li>サージ電圧抑制効果あり。</li> <li>スナバ回路での発生損失が少ない。</li> <li>放電阻止形RCDスナバ回路のスナバ抵抗における発生損失は下式で求められる。</li> </ul> $P = \frac{L_S \cdot I_0^2 \cdot f}{2}$ <p> <math>L_S</math> : 主回路の浮遊インダクタンス<br/> <math>I_0</math> : IGBTのターンオフ時コレクタ電流<br/> <math>f</math> : スイッチング周波数         </p>                                                                                                                                                              |

表5-4 一括スナバ回路の接続図

| スナバ回路接続図                                                                                       | 特 性(注意事項)                                                                                                      |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Cスナバ回路<br>    | <ul style="list-style-type: none"> <li>最も簡易的な回路</li> <li>主回路インダクタンスとスナバコンデンサによるLC共振回路により電圧が振動しやすい。</li> </ul>  |

| RCDスナバ回路<br> | <ul style="list-style-type: none"> <li>スナバダイオードの選定を誤ると高いサーボ電圧が発生することや、スナバダイオードの逆回復時に電圧が振動することがあります。</li> </ul> |

## 2.3 放電阻止形RCDスナバ回路の設計方法

IGBTのスナバ回路として、最も合理的と思われる放電阻止形RCDスナバ回路の基本的な設計方法について説明します。

### 2.3.1 適用可否の検討

図5-7に放電阻止形RCDスナバ回路を適用した場合のターンオフ時の動作軌跡を示します。

図5-7 ターンオフ時の動作軌跡

図5-8にターンオフ時の電流・電圧波形を示します。放電阻止形RCDスナバはIGBTの $V_{CE}$ が直流電源電圧を超えてから動作し、その理想的な動作軌跡は点線で示されています。

しかし実際の装置ではスナバ回路の配線インダクタンスやスナバダイオード過渡順電圧降下の影響によるターンオフ時のサージ電圧が存在するため、実線のように膨らみます。

図5-8 ターンオフ時の電流・電圧波形

放電阻止形RCDスナバ回路を適用するためには、適用後のターンオフ動作軌跡がIGBTのRB SOA内に収まっているか検証する必要があります。

なお、ターンオフ時のサージ電圧は次式で求められます。

$$V_{CESP} = E_d + V_{FM} + \left( -L_s \cdot \frac{dI_c}{dt} \right)$$

$E_d$  : 直流電源電圧

$V_{FM}$  : スナバダイオード過渡順電圧降下※

※ スナバダイオードの一般的な過渡順電圧降下の参考値は下記の通りです。

600Vクラス: 20~30V

1200Vクラス: 40~60V

$L_s$  : スナバ回路の配線インダクタンス

$dI_c/dt$  : ターンオフ時のコレクタ電流変化率最大値

### 2.3.2 スナバコンデンサ( $C_s$ )容量値の求め方

スナバコンデンサに必要な容量値は次式で求められます。

$$C_s = \frac{L_s \cdot I_0^2}{(V_{CEP} - E_d)^2}$$

$L_s$  : 主回路の配線インダクタンス

$I_0$  : IGBTのターンオフ時コレクタ電流

$V_{CEP}$  : スナバコンデンサ電圧の最終到達値

$E_d$  : 直流電源電圧

$V_{CEP}$ はIGBTの $V_{CES}$ 以下に抑える必要があります。また、スナバコンデンサには高周波特性の良いもの(フィルムコンデンサなど)を選んでください。

### 2.3.3 スナバ抵抗( $R_s$ )値の求め方

スナバ抵抗への要求機能は、IGBTが次のターンオフ動作を行うまでにスナバコンデンサの蓄積電荷を放電する事です。IGBTが次のターンオフ動作を行うまでに、蓄積電荷の90%を放電する条件でスナバ抵抗を求めるとき式のようになります。

$$R_s \leq \frac{1}{2.3 \cdot C_s \cdot f}$$

$R_s$  : スナバ抵抗

$C_s$  : スナバコンデンサ容量

$f$  : スイッチング周波数

スナバ抵抗値をあまりにも低い値に設定すると、スナバ回路電流が振動しIGBTのターンオン時のコレクタ電流尖頭値も増えるので、式を満足する範囲内で極力高い値に設定してください。

スナバ抵抗の発生損失 $P(R_s)$ は抵抗値と関係なく次式で求められます。

$$P(R_s) = \frac{L_s \cdot I_0^2 \cdot f}{2}$$

$P(R_s)$  : スナバ抵抗の発生損失

$L_s$  : 主回路の配線インダクタンス

$I_0$  : IGBTのターンオフ時コレクタ電流

$f$  : スイッチング周波数

#### 2.3.4 スナバダイオードの選定

スナバダイオードの過渡順電圧降下は、ターンオフ時のサージ電圧発生要因の一つになります。またスナバダイオードの逆回復時間が長いと、高周波スイッチング動作時にスナバダイオードの発生損失が大きくなり、スナバダイオードの逆回復が急激であると、スナバダイオードの逆回復動作時にIGBTのC-E間電圧が急激に大きく振動します。スナバダイオードには、過渡順電圧が低く、逆回復時間が短く、逆回復動作がソフトなものを選んでください。

#### 2.3.5 スナバ回路配線上の注意事項

スナバ回路の $L_S$ はサージ電圧発生要因となりますので、回路部品の配置も含めてインダクタンス低減の工夫を行ってください。

## 2.4 サージ電圧抑制回路 ークランプ回路構成例ー

一般的に、主回路インダクタンスの低減やスナバ回路を設けることによってC-E間のサージ電圧を抑制することができます。しかしながら装置の運転条件などによってはサージ電圧の抑制が困難な場合があります。このような場合に用いられるサージ電圧抑制回路の1つとしてアクティブクランプ回路があります。

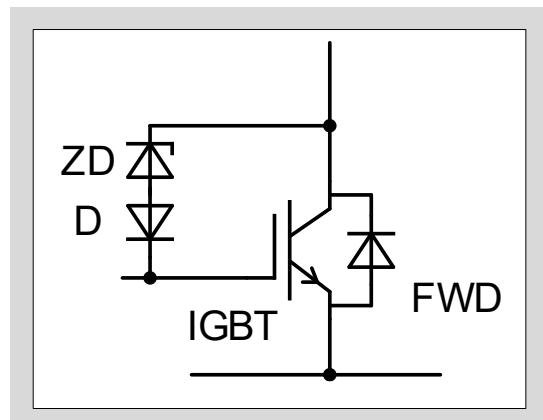

図5-9にアクティブクランプ回路の一例を示します。基本的な回路構成は、C-G間にツエナーダイオードを付加するとともに、そのツエナーダイオードと逆通電方向にダイオードを直列に接続しています。

この回路でC-E間にツエナーダイオードの降伏電圧を超える電圧が発生した場合、ツエナーダイオードが降伏しコレクタからゲートに電流が流れます。この電流と $R_G$ によりG-E間に+電圧が加わります。 $+V$ がIGBTのG-E間しきい値電圧 $V_{GE(th)}$ を超えるとIGBTに $I_C$ が流れ、 $V_{CE}$ はツエナーダイオードの降伏電圧と概ね等しくなるようにクランプします。アクティブクランプ回路を設けることでサージ電圧抑制が可能となります。

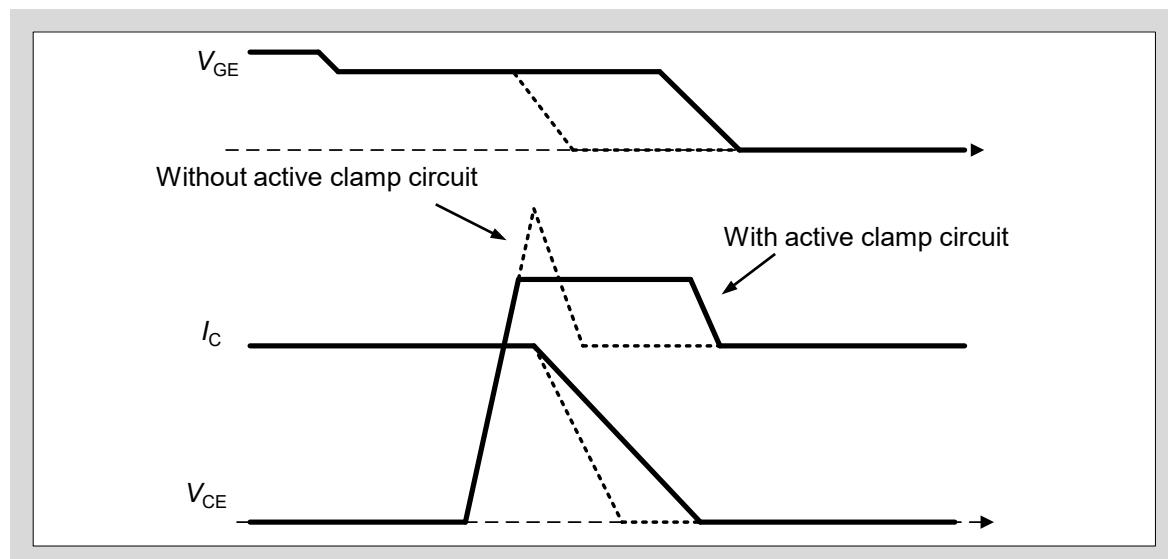

一方、ツエナーダイオードの降伏電流はIGBTをオンさせるために流れるため、ターンオフ時の電流変化率 $di/dt$ はクランプ回路付加前より緩やかになり、ターンオフ時間が長くなり(図5-10参照)、ターンオフ損失が増えますので、各種設計検証を行った上でクランプ回路を適用してください。

図5-9 アクティブクランプ回路例

図5-10 アクティブクランプ回路適用時の波形例

## 第6章 放熱設計方法

|                           |     |

|---------------------------|-----|

| 1. ディスクリートIGBTの発生損失       | 6-2 |

| 2. Fuji IGBTシミュレータについて    | 6-3 |

| 3. 昇圧チョッパ回路の発生損失計算方法      | 6-4 |

| 4. 三相2レベルインバータ回路の発生損失計算方法 | 6-5 |

| 5. 放熱の考え方                 | 6-9 |

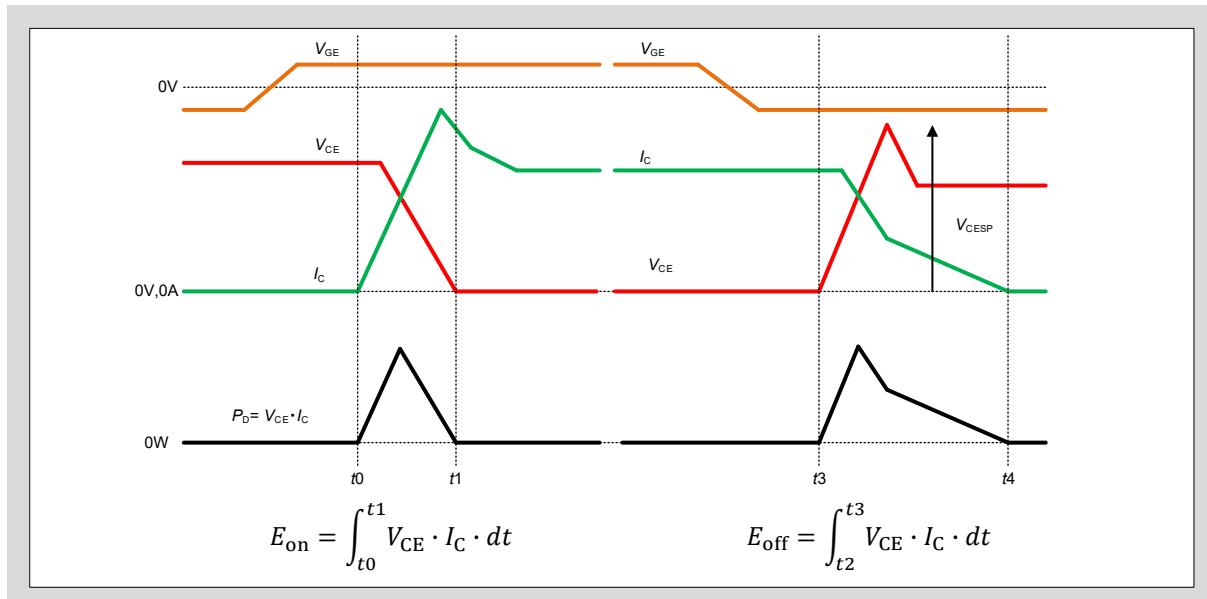

## 1. ディスクリートIGBTの発生損失

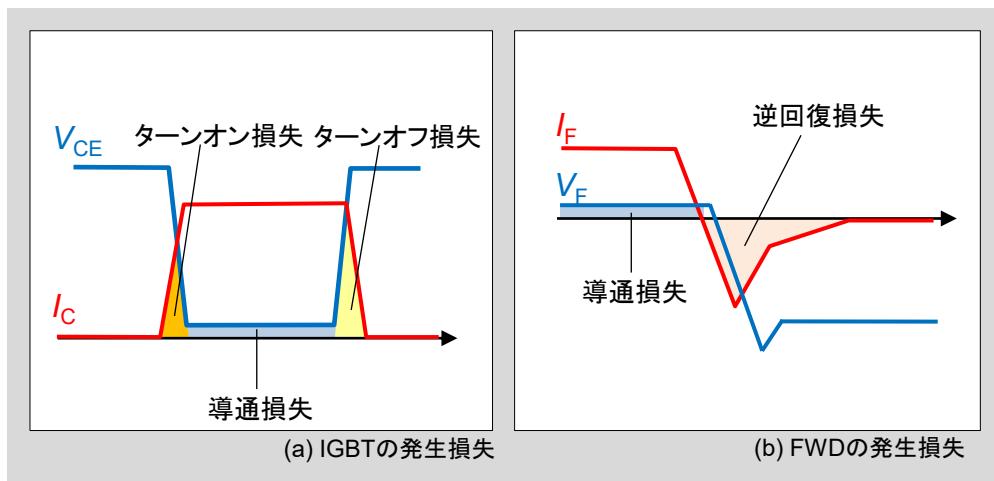

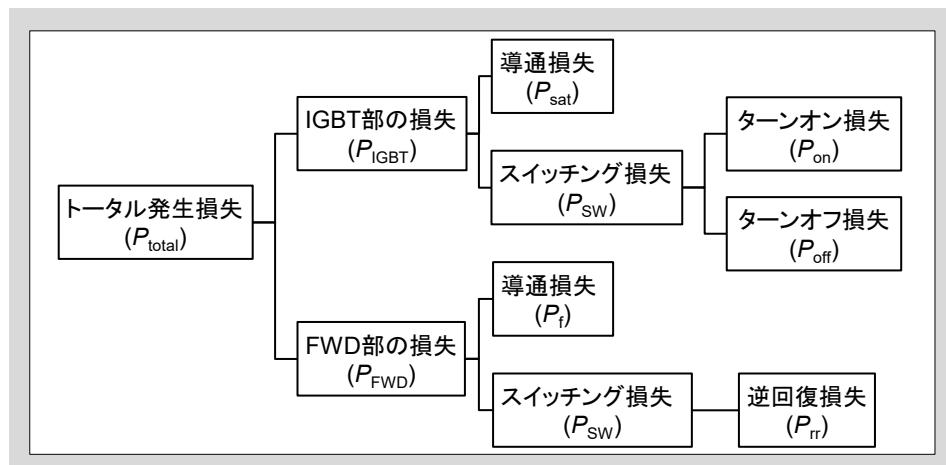

ディスクリートIGBTはIGBTのみの製品とIGBT+FWD構成の製品があります。後者の発生損失はIGBTとFWDの2つの発生損失を考慮する必要があります。また発生する損失は図6-1に示すように定常時の導通損失とスイッチング時のスイッチング損失があります。以上を整理すると図6-2のようになります。

図6-1 IGBTとFWDのスイッチング波形と発生損失

図6-2 ディスクリートIGBT発生損失の分類

IGBT部の導通損失はデータシートに記載のオン電圧-コレクタ電流特性( $V_{CE(sat)}$ - $I_C$ 特性)から、FWD部の導通損失はオン電圧-順方向電流特性( $V_F$ - $I_F$ 特性)から計算します。また、各スイッチング損失はスイッチングエネルギー-コレクタ電流/順方向電流特性( $E_{on}$ - $I_C$ ,  $E_{off}$ - $I_C$ ,  $E_{rr}$ - $I_C$ 特性)から計算します。これらの発生損失から放熱設計を行い、素子の接合部温度 $T_{vj}$ が定格を超えないようにします。なお、ここで使用するオン電圧やスイッチング損失の値には、 $T_{vj}$ が高温時のデータを使用して計算してください。

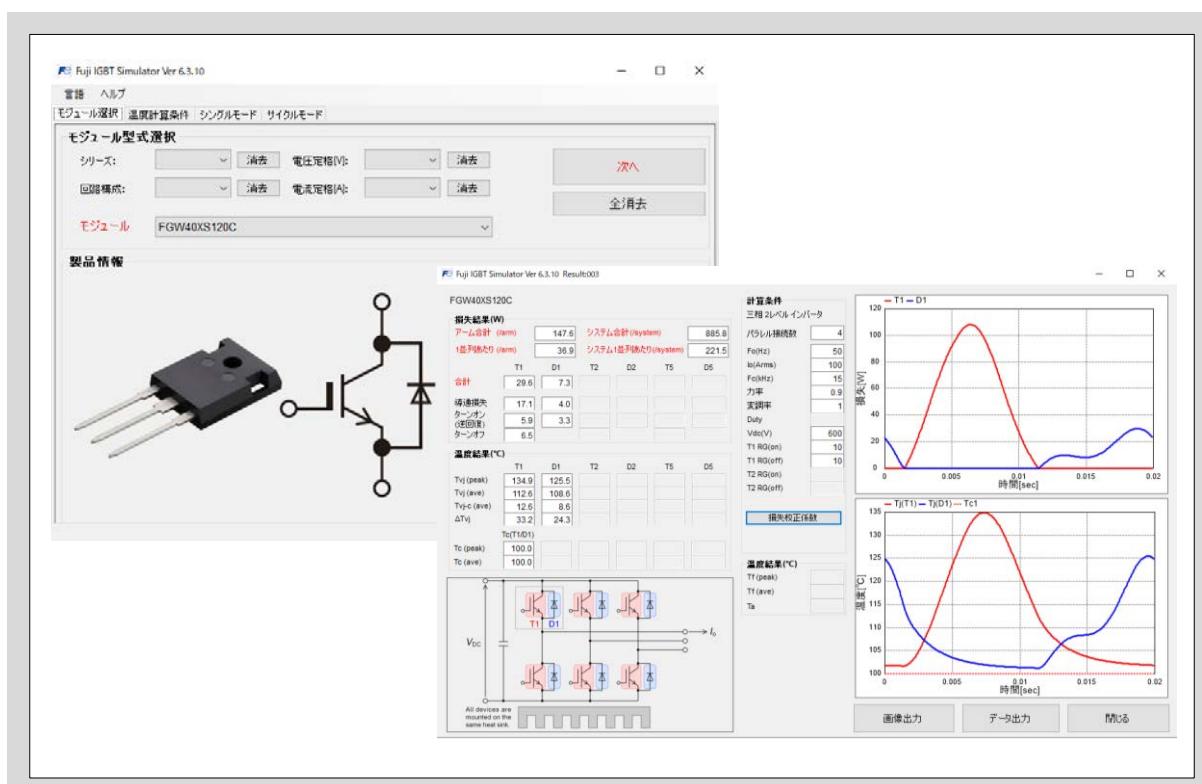

## 2. Fuji IGBTシミュレータについて

ウェブサイトでは、ディスクリートIGBTの発生損失や接合部温度を計算するツールとしてFuji IGBTシミュレータ\*を公開しています。Fuji IGBTシミュレータでは、データシートの特性カーブをより精度よく近似し、また素子接合部温度依存性も考慮した計算を行うことができます。使用方法については、ウェブサイトに掲載のユーザマニュアルをご参照ください。

しかし、製品や回路によってはFuji IGBTシミュレータで計算を行うことができない場合があります。その際は、損失を手計算で行う必要があります。次項以降で発生損失の計算方法について述べますので、内容を参考にして計算を行ってください。

図6-3 Fuji IGBT シミュレータの使用例

\* Fuji IGBTシミュレータ: [www.fujielectric.co.jp/products/semiconductor/model/power\\_modules/igbt/simulation/](http://www.fujielectric.co.jp/products/semiconductor/model/power_modules/igbt/simulation/)

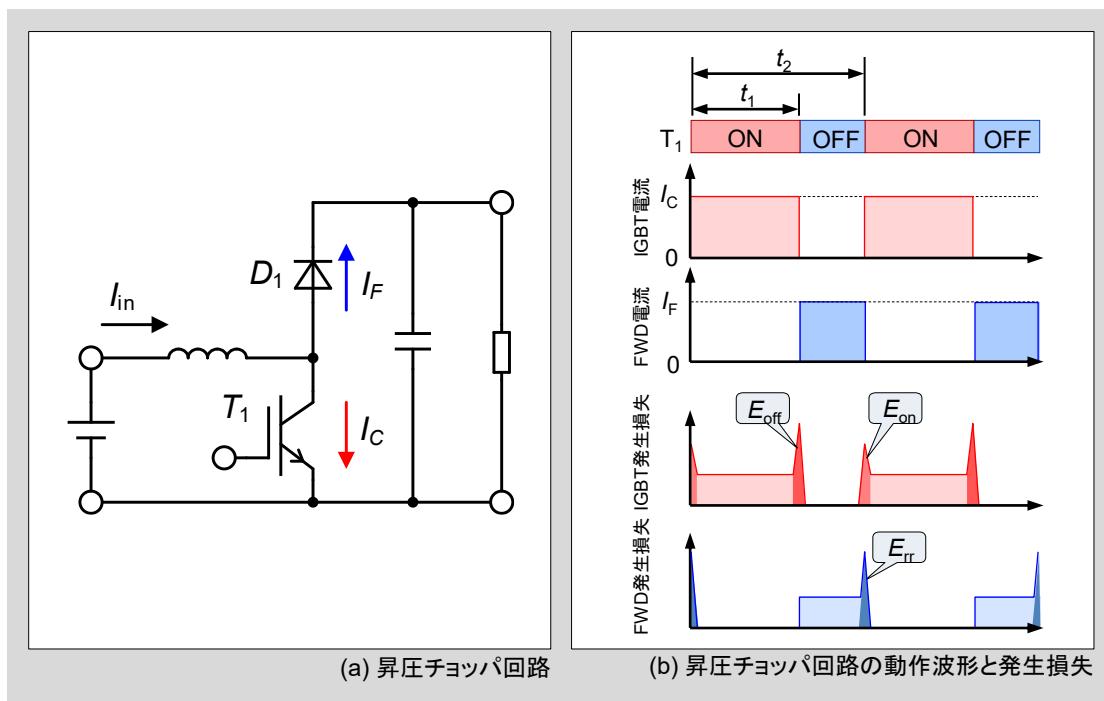

### 3. 昇圧チョッパ回路の発生損失計算方法

図6-4に示すような昇圧チョッパ回路の場合、IGBT( $T_1$ )およびFWD( $D_1$ )に流れる電流を矩形波の連続と考えれば、 $T_1$ 、 $D_1$ の単位時間当たりの発生損失(単位:W)は以下の式で近似計算することができます。

$$P_{\text{IGBT}} = \text{導通損失} + \text{ターンオン損失} + \text{ターンオフ損失}$$

$$= V_{\text{CE(sat)}} \cdot I_C \cdot d + (E_{\text{on}} + E_{\text{off}}) \cdot f_C \cdot \left(\frac{V_{\text{CC}}}{V_{\text{CC0}}}\right)^{\alpha} \quad \dots \dots \dots (1)$$

$$P_{\text{FWD}} = \text{導通損失} + \text{逆回復損失}$$

$$= V_F \cdot I_F \cdot (1 - d) + E_{\text{rr}} \cdot f_C \cdot \left(\frac{V_{\text{CC}}}{V_{\text{CC0}}}\right)^{\alpha} \quad \dots \dots \dots (2)$$

ただし、

$d$  : IGBTのオンデューティ =  $t_1 / t_2$

$f_C$  : キャリア周波数(スイッチング周波数) =  $1 / t_2$

$V_{\text{CC}}$  : 電源電圧

$V_{\text{CC0}}$  : データシートに記載しているスイッチング電圧

$\alpha$  : スイッチングエネルギーのスイッチング電圧依存性係数

スイッチングエネルギーがスイッチング電圧に比例するとみなせば、 $\alpha = 1$ とすることができます。

一方 $V_{\text{CE(sat)}}$ 、 $V_F$ 、 $E_{\text{on}}$ 、 $E_{\text{off}}$ 、 $E_{\text{rr}}$ の値は素子の $T_{\text{vj}}$ に依存し、 $E_{\text{on}}$ 、 $E_{\text{off}}$ 、 $E_{\text{rr}}$ の値はゲート抵抗値 $R_G$ によっても変化しますので、データシートのグラフを参考に換算を行ってください。

図6-4 昇圧チョッパ回路での発生損失

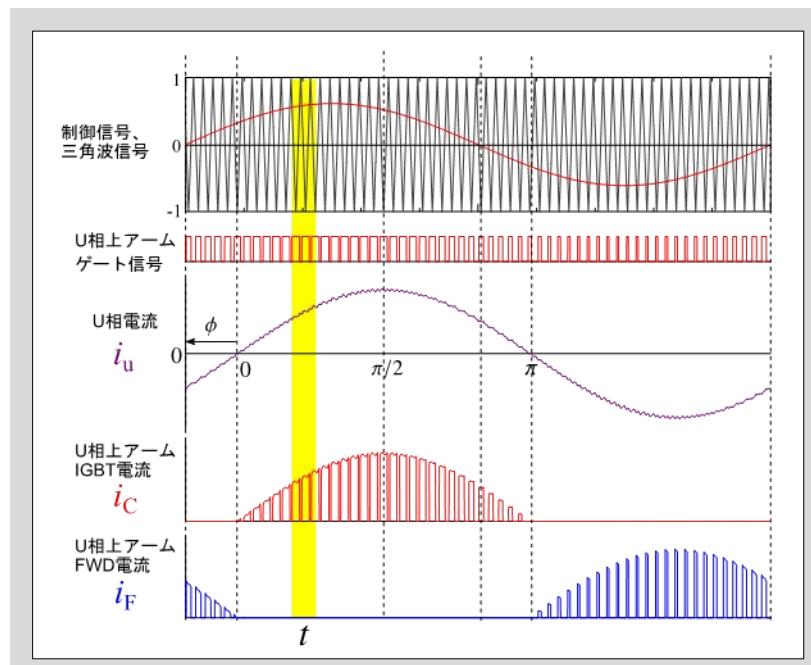

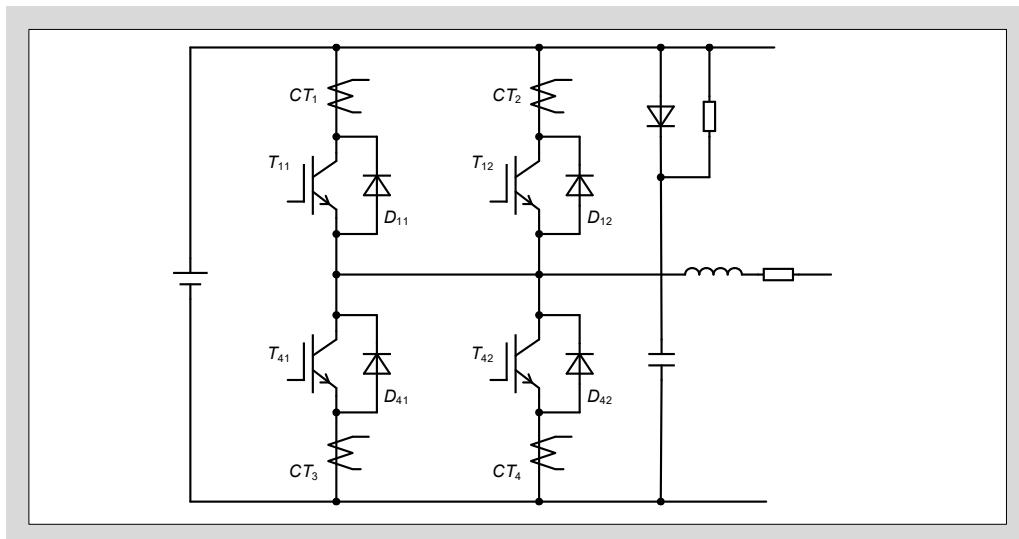

## 4. 三相2レベルインバータ回路の発生損失計算方法

三相2レベル電圧型インバータでPWM制御を行う場合の損失計算は図6-5に示すようにIGBTやFWDに流れる電流値や動作条件が常に変化しているため、発生損失を正確に計算するには複雑な計算が必要になります。ここではディスクリートIGBTの特性カーブ近似式を用いてインバータ回路でのIGBT/FWDの発生損失を簡易的に計算する方法を紹介します。

計算を行うにあたり、以下の条件を前提とします。

- PWM 制御三相 2 レベルインバータであること

- PWM は三角波比較の正弦波変調方式であること

- 出力電流は理想的な正弦波であること

インバータの出力相電流の実効値を $I_0$ とすると正弦波の電流波形は以下の式で表されます。

$$i_0(\theta) = \sqrt{2} \cdot I_0 \cdot \sin \theta \quad \dots \dots \dots (3)$$

またIGBTのオンデューティ波形 $d(\theta)$ は、変調率を $m$ 、電流の遅れ力率を $\cos\phi$ とすると以下の式で表されます。

$$d(\theta) = \frac{1 + m \cdot \sin(\theta + \phi)}{2} \quad \dots \dots \dots (4)$$

図6-5 正弦波変調2レベルインバータの動作波形

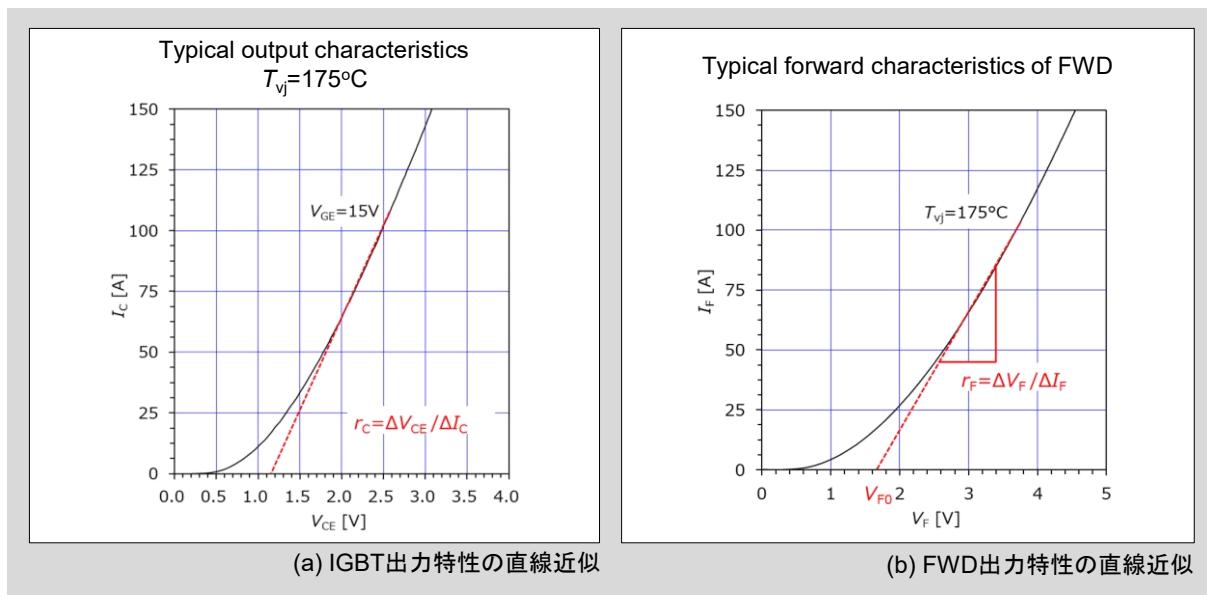

IGBTに $I_C$ が流れると、コレクタ-エミッタ間に $V_{CE(sat)}$ が発生します。 $V_{CE(sat)}$ は $I_C$ に依存し、その依存性グラフはデータシートに記載されています。インバータにおけるIGBTの導通損失を計算するために、この $V_{CE(sat)}$ の $I_C$ 依存性を図6-6で示すように直線近似した場合、以下の式で表されます。

$$V_{CE(sat)} = r_C \cdot I_C + V_{CEO} \quad \dots \dots \dots (5)$$

同様に、FWDのオン電圧 $V_F$ の順電流 $I_F$ 依存性も直線近似した場合、以下の式で表されます。

$$V_F = r_F \cdot I_F + V_{FO} \quad \dots \dots \dots (6)$$

図6-6 出力特性の近似

(3)式、(4)式および(5)式より、インバータ回路での1アームあたりのIGBTの導通損失 $P_{sat}$ は、

$$\begin{aligned} P_{sat} &= \frac{1}{2\pi} \int_0^\pi \{i_O(\theta) \cdot V_{CEsat}(\theta) \cdot d(\theta)\} d\theta \\ &= 2I_0^2 \cdot r_C \left( \frac{1}{8} + \frac{m}{3\pi} \cos \varphi \right) + \sqrt{2} \cdot I_0 \cdot V_{CEO} \left( \frac{1}{2\pi} + \frac{m}{8} \cos \varphi \right) \end{aligned} \quad \dots \dots \dots (7)$$

と求められます。同様にして、1アームあたりのFWDの導通損失 $P_f$ は、

$$\begin{aligned} P_f &= \frac{1}{2\pi} \int_\pi^{2\pi} \{-i_O(\theta) \cdot V_F(\theta) \cdot d(\theta)\} d\theta \\ &= 2I_0^2 \cdot r_F \left( \frac{1}{8} - \frac{m}{3\pi} \cos \varphi \right) + \sqrt{2} \cdot I_0 \cdot V_{FO} \left( \frac{1}{2\pi} - \frac{m}{8} \cos \varphi \right) \end{aligned} \quad \dots \dots \dots (8)$$

と求められます。

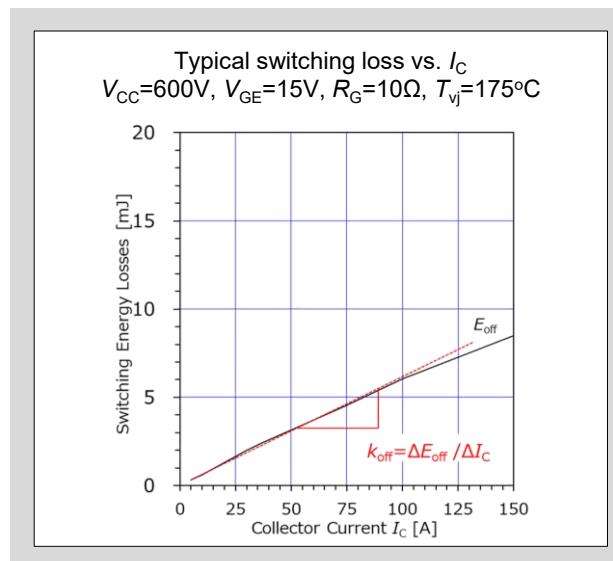

次に、スイッチング損失を計算するために、データシートに記載されている $E_{on}$ 、 $E_{off}$ 、 $E_{rr}$ の $I_C$ 依存性グラフの近似式を求めます。図6-7に示すように、スイッチングエネルギーの $I_C$ 依存性カーブを直線近似し、スイッチング電圧依存性係数 $\alpha=1$ とすると $E_{on}$ 、 $E_{off}$ 、 $E_{rr}$ はそれぞれ以下の式で表すことができます。

$$E_{on}(I_C) = k_{on} \cdot I_C \cdot \left( \frac{V_{CC}}{V_{CC0}} \right) \quad \dots \dots \dots (9)$$

$$E_{off}(I_C) = k_{off} \cdot I_C \cdot \left( \frac{V_{CC}}{V_{CC0}} \right) \quad \dots \dots \dots (10)$$

$$E_{rr}(I_F) = k_{rr} \cdot I_F \cdot \left( \frac{V_{CC}}{V_{CC0}} \right) \quad \dots \dots \dots (11)$$

図6-7 スイッチングエネルギーの $I_C$ 依存性の近似

(9)式を用いて、インバータ回路における1アームあたりのIGBTのターンオン損失 $P_{on}$ は以下の式で求められます。

$$P_{\text{on}} = \frac{1}{2\pi} \int_0^\pi \left\{ k_{\text{on}} (\sqrt{2} \cdot I_o \cdot \sin \theta) \cdot \frac{V_{\text{CC}}}{V_{\text{CC0}}} \cdot f_{\text{SW}} \right\} d\theta$$

$$= \frac{\sqrt{2}}{\pi} k_{\text{on}} \cdot I_o \cdot \frac{V_{\text{CC}}}{V_{\text{CC0}}} \cdot f_{\text{SW}} \quad \dots \quad (12)$$

同様にして、ターンオフ損失 $P_{\text{off}}$ 、FWDの逆回復損失 $P_{\text{rr}}$ は以下の式で計算できます。

$$P_{\text{off}} = \frac{\sqrt{2}}{\pi} \cdot k_{\text{off}} \cdot I_0 \cdot \frac{V_{\text{CC}}}{V_{\text{CC0}}} \cdot f_{\text{SW}} \quad \dots \quad (13)$$

$$P_{rr} = \frac{\sqrt{2}}{\pi} \cdot k_{rr} \cdot I_0 \cdot \frac{V_{CC}}{V_{CC0}} \cdot f_{SW} \quad \dots \quad (14)$$

以上の計算より、1アームあたりのIGBT部の発生損失 $P_{IGBT}$ 、FWD部の発生損失 $P_{FWD}$ は以下のように計算できます。

$$P_{\text{JGBT}} = P_{\text{sat}} + P_{\text{on}} + P_{\text{off}} \quad \dots \quad (15)$$

実際には、6.2項でも述べたように $V_{CE(sat)}$ 、 $V_F$ 、 $E_{on}$ 、 $E_{off}$ 、 $E_{rr}$ の値は $T_{vj}$ や $R_G$ に依存して変化しますので、データシートに記載されている $T_{vj}$ 依存性グラフや $R_G$ 依存性グラフを参考に換算して計算してください。

## 5. 放熱の考え方

放熱設計では、発生損失をもとに許容温度以下となるようなヒートシンクの選定を行います。放熱設計が十分でない場合、実機運転中等に素子の許容温度を超えて破壊するといった問題が発生する可能性があります。

### 5.1 過渡熱インピーダンスと定常熱抵抗

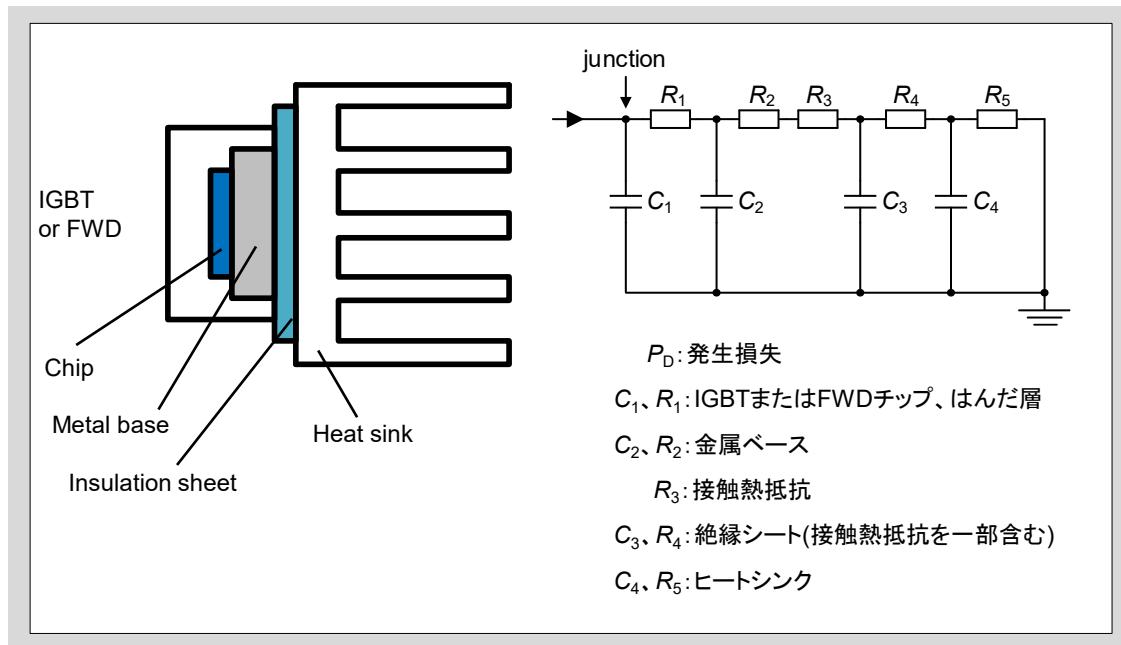

素子の接合部で発生する損失の放熱処理は、ヒートシンクに取付ける場合は図6-8に放熱経路を便宜的に電気的等価回路で模擬したものを見ます。

図6-8 热挙動の電気的等価回路

過渡熱インピーダンスは図6-8の等価回路で、熱容量 $C_1 \sim C_4$ の影響がある時間範囲のインピーダンスであり、時間の関数です。各素子の過渡熱インピーダンス特性は、データシートにその最大値が明記され、繰り返し率D=0がそれに当たります。またヒートシンクの過渡熱インピーダンスは次式で得られます。

$$R_{f(t)} = R_{th(f-a)} \left( 1 - e^{-\frac{t}{\tau f}} \right)$$

ただし、 $\tau f = R_{th(f-a)} \cdot V \cdot \gamma \cdot C$

$R_{th(f-a)}$ : ヒートシンク定常熱抵抗[°C/W]

$t$ : 時間[sec]

$\tau f$ : ヒートシンクの熱時定数[sec]

$V$ : ヒートシンク体積[cm<sup>3</sup>]

$\gamma$ : 比重[g / cm<sup>3</sup>]

$C$ : 比熱[J / g · deg]

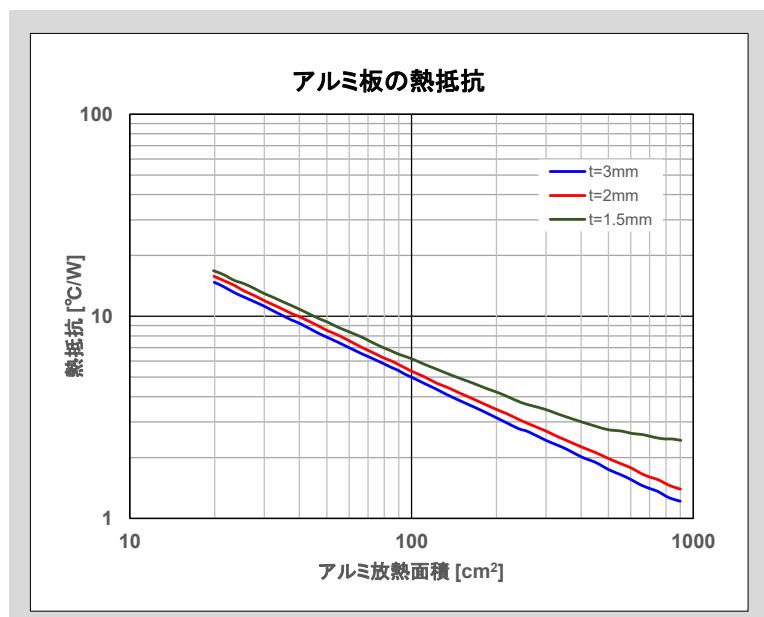

この計算に必要な材料の比重と比熱を表6-1に、アルミヒートシンク(黒色塗装)の定常熱抵抗を図6-9に示します。

表6-1 各材料の比重と比熱

| 材料     | 比重γ<br>[g/cm <sup>3</sup> ] | 比熱<br>[J/g・deg] |

|--------|-----------------------------|-----------------|

| アルミニウム | 2.71                        | 0.895           |

| 銅      | 8.96                        | 0.383           |

図6-9 アルミヒートシンクの定常熱抵抗

## 5.2 定常状態の熱方程式

定常熱抵抗は熱容量の影響が全くなくなった以降の熱抵抗であり、素子接合部温度は簡単に求めることができます。

$$T_{vj} = T_a + P_D \cdot (R_{th(j-c)} + R_{th(c-i)} + R_{th(i)} + R_{th(i-f)} + R_{th(f-a)})$$

- $T_{vj}$  : 接合部温度

- $T_a$  : 周囲温度

- $R_{th(j-c)}$  : 接合部-ケース間熱抵抗 (IGBTまたはFWD)

- $R_{th(i)}$  : 絶縁シート熱抵抗

- $R_{th(c-i)}, R_{th(i-f)}$  : 接触熱抵抗

- $R_{th(f-a)}$  : ヒートシンク熱抵抗

- $P_D$  : 発生損失

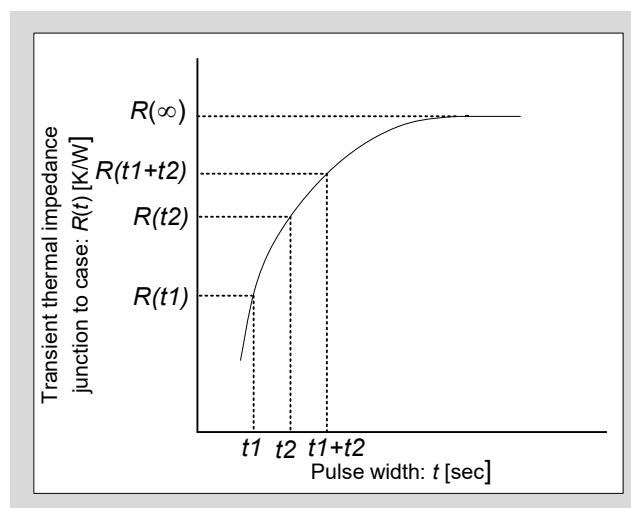

### 5.3 過渡状態の熱方程式

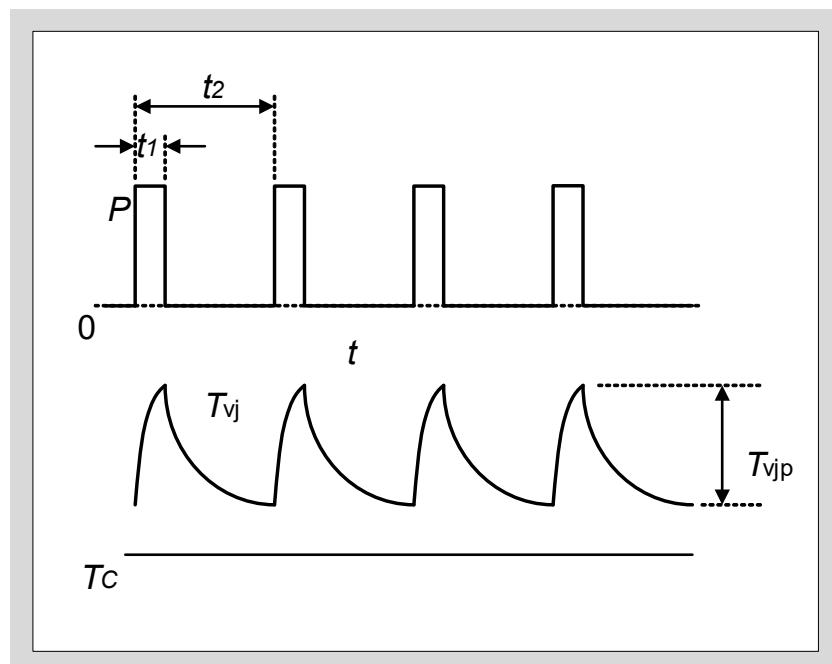

一般的には前述のように平均発生損失から定常状態の  $T_{vj}$  を考えれば十分ですが、実際にはスイッチングを繰り返すごとに損失はパルス状に発生しますので図6-11に示すように温度リップルを生じます。この場合、発生損失を一定周期かつ一定ピーク値の連続矩形波パルスと考えれば仕様書記載の過渡熱抵抗曲線例(図6-10)を使用して温度リップルのピーク値  $T_{vjp}$  を近似的に下記式にて計算することができます。

この  $T_{vjp}$  も  $T_{vj\max}$  を超えないことを確認して使用してください。

$$T_{vjp} - T_c = P \cdot [R_{(\infty)} \cdot \frac{t_1}{t_2} + R_{(t_1+t_2)} \cdot (1 - \frac{t_1}{t_2}) - R_{(t_2)} + R_{(t_1)}]$$

図6-10 過渡熱抵抗曲線例

図6-11 温度リップル

## 第7章 ゲート駆動回路設計方法

|                       |      |

|-----------------------|------|

| 1. ゲート駆動条件と主要特性の関係    | 7-2  |

| 2. ゲート駆動電流について        | 7-6  |

| 3. デッドタイムの設定          | 7-7  |

| 4. ゲート駆動回路設計の具体例      | 7-9  |

| 5. ゲート駆動回路設計、実装上の注意事項 | 7-10 |

本章では、ディスクリートIGBTのゲート駆動回路設計手法について説明します。

## 1. ゲート駆動条件と主要特性の関係

表7-1にIGBTのゲート駆動条件と主要特性の一般的な関係を示します。IGBTの主要特性はG-E間電圧 $V_{GE}$ 、ゲート抵抗 $R_G$ により変化するので装置の設計目標にあわせた設定が必要です。

表7-1 IGBTのゲート駆動条件と主要特性

| 主要特性                   | + $V_{GE}$ 増 | - $V_{GE}$ 増 | $R_{G(ON)}$ 増 | $R_{G(OFF)}$ 増 |

|------------------------|--------------|--------------|---------------|----------------|

| $V_{CE(sat)}$          | ↓            | —            | —             | —              |

| $t_{on}$<br>$E_{on}$   | ↓            | —            | ↑             | —              |

| $t_{off}$<br>$E_{off}$ | —            | ↓            | —             | ↑              |

| ターンオン<br>FWDサージ電圧      | ↑            | —            | ↓             | —              |

| ターンオフ<br>IGBTサージ電圧     | —            | ↑            | —             | ↓*1            |

| dV/dt誤点弧               | ↑            | ↓            | ↓             | ↓              |

| 飽和電流値                  | ↑            | —            | —             | —              |

| 短絡耐量 *2                | ↓            | —            | —             | —              |

| 放射ノイズ                  | ↑            | —            | ↓             | ↓              |

\*1 シリーズによってサージ電圧のゲート抵抗依存性は異なります。

\*2 XSシリーズでは短絡耐量を保証しておりません。

### 1.1 ゲート順バイアス電圧 :+ $V_{GE}$ (オン期間)

ゲート順バイアス電圧+ $V_{GE}$ の推奨値は+15Vです。以下に+ $V_{GE}$ 設計時の留意事項を示します。

- + $V_{GE}$ はG-E間最大定格電圧20V以下で設計してください。

- 電源電圧の変動は±10%以内を推奨します。

- オン期間中のC-E間飽和電圧( $V_{CE(sat)}$ )は+ $V_{GE}$ によって変化し、+ $V_{GE}$ が高い程低くなります。

- ターンオンスイッチング時の時間や損失は+ $V_{GE}$ が高い程小さくなります。

- ターンオン時(FWD逆回復時)の対向アームのサージ電圧は+ $V_{GE}$ が高い程発生しやすくなります。

- IGBTがオフ期間中でもFWDの逆回復時のdV/dtにより誤動作し、パルス状の短絡電流が流れて過剰な発熱や最悪の場合破壊を招くことがあります。この現象はdV/dt誤点弧と呼ばれ、+ $V_{GE}$ が高い程発生しやすくなります。

- + $V_{GE}$ が高い程、飽和電流が大きくなります。

### 1.2 ゲート逆バイアス電圧 : $-V_{GE}$ (オフ期間)

$dV/dt$ 誤点弧防止方法として $-V_{GE}$ を印加する方法が挙げられます。以下に $-V_{GE}$  設定時の留意事項を示します。

- $-V_{GE}$ はG-E間最大定格電圧-20V以内で設計してください。

- 電源電圧の変動は±10%以内を推奨します。

- IGBTのターンオフ特性は $-V_{GE}$ に依存し、特にコレクタ電流 $I_C$ がオフし始める部分の特性は $-V_{GE}$ に強く依存します。従って、ターンオフスイッチング時の時間や損失は $-V_{GE}$ が大きい程小さくなります。

### 1.3 ゲート抵抗: $R_G$

$R_G$ は回路構成や使用環境によって適切に変更する必要があります。以下に、 $R_G$ 設計時の留意事項を示します。

- スイッチング特性はターンオン、ターンオフ共に $R_G$ の大きさに依存し、 $R_G$ が大きいほどスイッチング時間やスイッチング損失は大きくなります。これに対し、一般的には $R_G$ が大きいほどスイッチング時のサージ電圧は小さくなると言われていますが、デバイスの構造により $R_G$ が大きくなるとサージ電圧が増加する場合があります。サージ電圧の $R_G$ 依存性の詳細は当社ウェブサイトに掲載されている技術資料を確認してください。

- $dV/dt$ 誤点弧は $R_G$ が大きい方が発生しにくくなります。

- 各種スイッチング特性は回路構成上の寄生インダクタンスなどにより大きく変動します。特にターンオフ時に発生するサージ電圧、FWDの逆回復時に発生するサージ電圧は大きく影響しますので、回路の寄生インダクタンスを可能な限り小さくした状態で、 $R_G$ を設計してください。

以上の各種特性のゲート抵抗依存性に注意しながら最適なゲート駆動条件を選定してください。

#### 1.4 FWD逆回復時のdv/dtによる誤点弧の回避方法

本節では、FWDの逆回復時のdv/dtによるIGBTのゲート誤点弧の原理と、誤点弧を回避する方法について説明します。

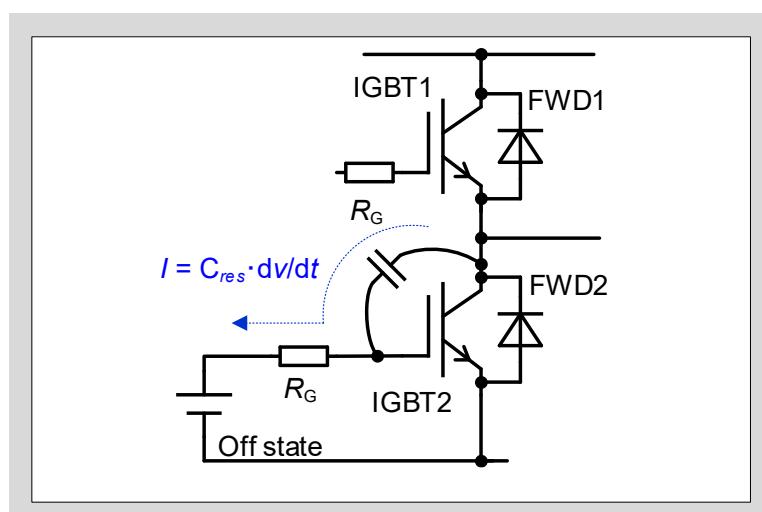

図7-1はdv/dt発生時に生じる誤点弧の原理について示した図です。本図ではIGBT1がオフ状態からオン状態に遷移するものとし、IGBT2はゲートを逆バイアスにしているものとします。IGBT1がオフ状態からオン状態になるとその対向アームのFWD2が逆回復します。また同時にオフ状態にあるIGBT2(FWD2)のコレクタ電位が上昇するため、IGBT1のターンオンに応じたdv/dtが発生します。IGBT1、IGBT2にはそれぞれ帰還容量 $C_{res}$ があるため、 $C_{res}$ を介して電流 $I = C_{res} \cdot dv/dt$ が流れます。この電流が $R_G$ に流れることより、 $V_{GE}$ が上昇します。 $V_{GE}$ がIGBT2の逆バイアス電圧としきい値電圧 $V_{GE(th)}$ の和の電圧を越えるとIGBT2が誤点弧(オン)することになり、IGBT1とIGBT2は短絡状態となります。

図7-1 dv/dt発生時の誤点弧の原理

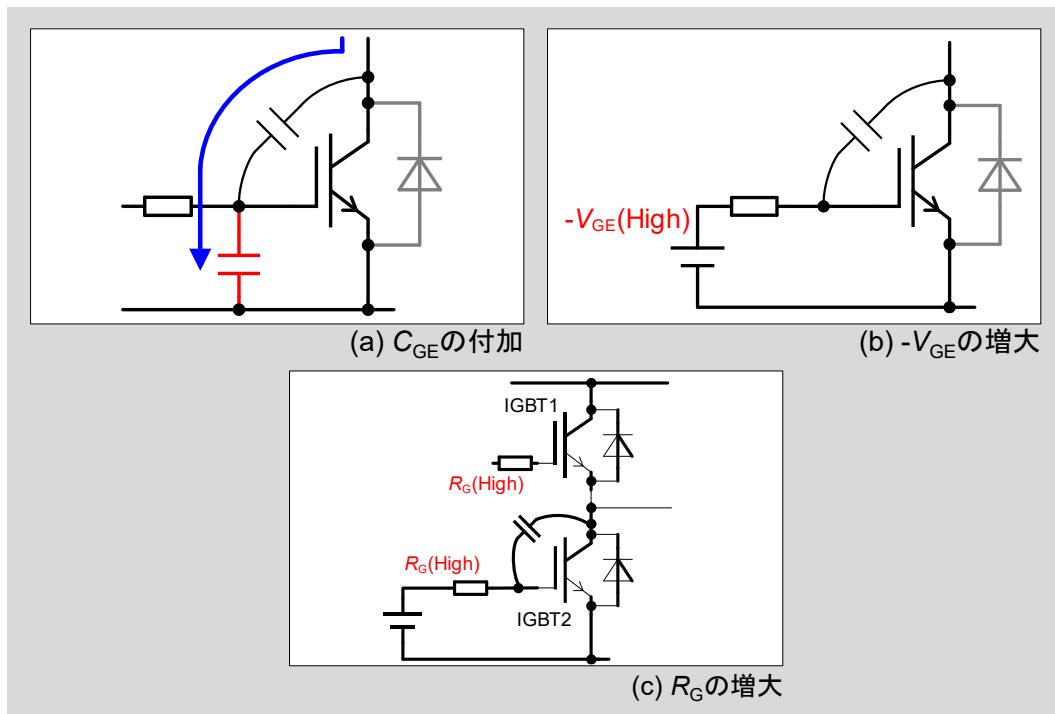

前述のように、IGBTは誤点弧を起こす場合があります。誤点弧を起こす場合、回避するための方法を図7-2に示します。IGBTの誤点弧回避方法として(a)G-E間に容量成分 $C_{GE}$ を付加し $V_{GE}$ の過渡的な上昇を抑制する方法、(b)- $V_{GE}$ を増やして $V_{GE}$ の過渡的上昇ピーク値を下げる方法、(c) $R_G$ を大きくして $dv/dt$ を下げる方法があります。これらの対策による効果は適用ゲート回路によって異なりますので、十分に確認して適用してください。またスイッチング損失への影響もありますので、併せて確認してください。

(a)G-E間に $C_{GE}$ を付加する方法は、誤点弧電流を $C_{GE}$ にバイパスすることによってゲート抵抗に流れる電流を低減させる方法です。しかし、 $C_{GE}$ を付加することでゲート駆動時に、この容量成分を充電する必要があるため、スイッチングスピードが遅くなり、スイッチング損失が大きくなります。一方で $C_{GE}$ を付加した場合でもゲート抵抗下げることでスイッチングスピードを適切にコントロールすることができます。すなわち適当な $C_{GE}$ と $R_G$ の組み合わせにすることで、スイッチング損失を増大させることなく誤点弧を回避することが可能です。なお $C_{GE}$ 、 $R_G$ の目安としては仕様書に記載の $C_{ies}$ に対し2倍程度をG-E端子間直近へ付加するとともに、 $R_G$ は $C_{GE}$ 付加前に対し概ね半分に変更することを推奨します。ただし、 $R_G$ 、 $C_{GE}$ の選定は適用側の評価により、十分に確認してください。

図7-2  $dv/dt$ 誤点弧回避方法

## 2. ゲート駆動電流について

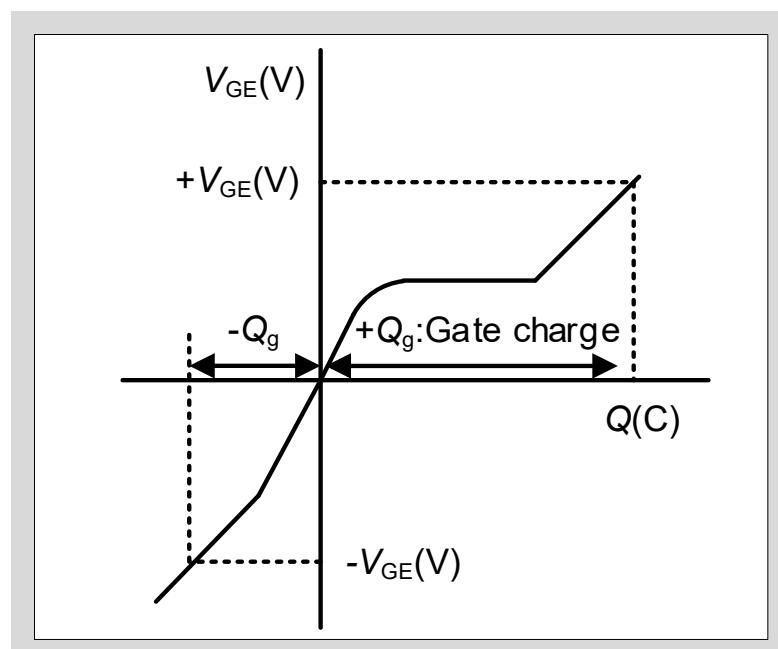

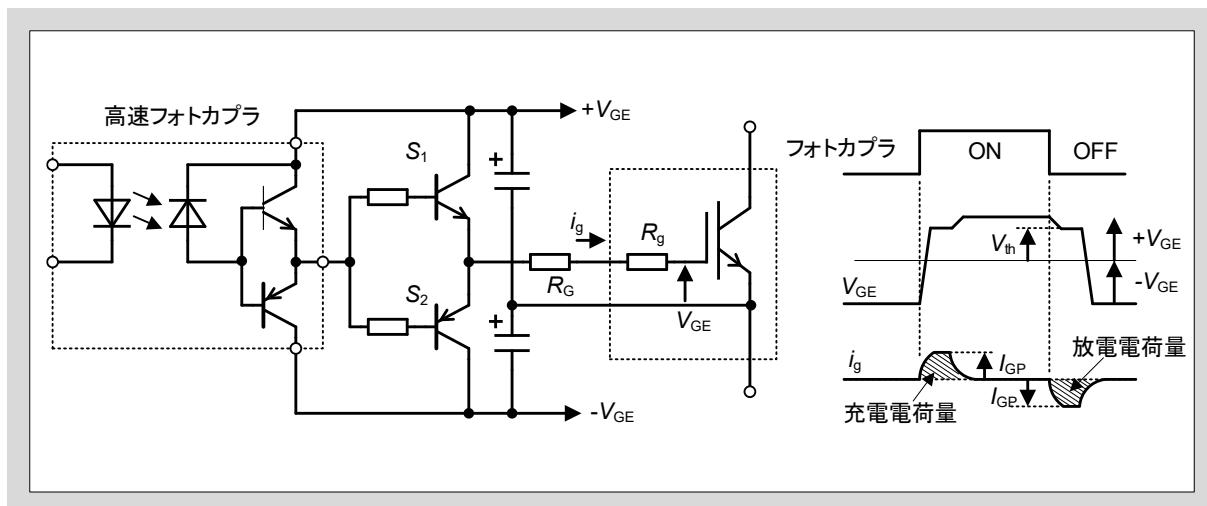

IGBTはMOSゲート構造を持っており、スイッチング時にこれを充放電するゲート電流(駆動電流)を流す必要があります。図7-3にゲート充電電荷量特性を示します。ゲート充電電荷量特性はIGBTを駆動するのに必要な電荷量を表しており、平均駆動電流や駆動電力の計算に使用できます。図7-4にゲート駆動回路の回路図と電圧電流波形を示します。駆動回路の原理は順バイアス電源と逆バイアス電源をスイッチS1・S2にて交互に切り換えるもので、切り換え時にゲートを充放電する電流が駆動電流であり、図7-4中の電流波形で表される面積(斜線部分)が図7-3中の充放電電荷量と等しくなります。

図7-3 ゲート充電電荷量特性(ダイナミック入力特性)の概略波形

図7-4 駆動回路原理図およびゲート電圧電流波形

駆動電流の尖頭値 $I_{GP}$ は次の近似式で求められます。

$$I_{GP} = \frac{|+V_{GE}| + |-V_{GE}|}{R_G}$$

$+V_{GE}$  : 順バイアス電源電圧

$-V_{GE}$  : 逆バイアス電源電圧

$R_G$  : 駆動回路のゲート抵抗

一方駆動電流の平均値 $I_G$ は図7-3に示したゲート電荷量特性を用いて次式にて計算できます。

$$+I_G = |-I_G| = f_C \cdot (|+Q_g| + |-Q_g|)$$

$f_C$  : キャリア周波数

$+Q_g$  : 0Vから $+V_{GE}$ までの電荷量

$-Q_g$  :  $-V_{GE}$ から0Vまでの電荷量

したがって、駆動回路の出力段にはこれらの近似式で計算した $I_{GP}$ 、および $\pm I_G$ を流せるように設計する必要があります。また、駆動回路の発生損失をすべて $R_G$ で全て消費するとすれば、IGBTを駆動するために必要な駆動電力 $P_d$ は次式で表されます。

$$P_{d(on)} = f_C \cdot \left[ \frac{1}{2} (|+Q_g| + |-Q_g|) \cdot (|+V_{GE}| + |-V_{GE}|) \right]$$

$$P_{d(off)} = P_{d(on)}$$

$$P_d = P_{d(off)} + P_{d(on)}$$

$$= f_C \cdot (|+Q_g| + |-Q_g|) \cdot (|+V_{GE}| + |-V_{GE}|)$$

したがって、 $R_G$ にはこの近似式で計算した発生損失を許容できるものを選定する必要があります。

以上に述べたような駆動電流、駆動電力を供給できるように駆動回路を設計してください。

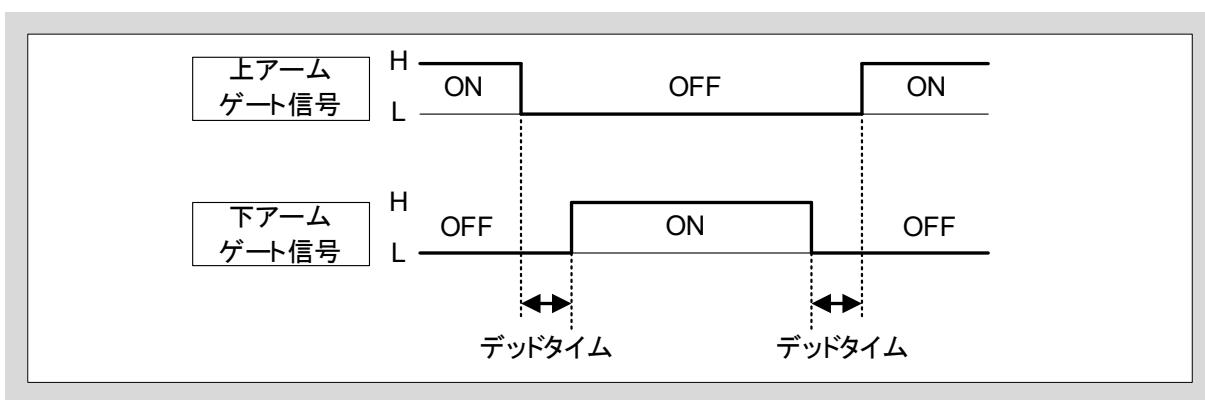

### 3. デッドタイムの設定

インバータ回路などでは、上下アームの短絡防止のため、オン・オフの切り換えタイミングにデッドタイムを設定する必要があります。図7-5に示すようにデッドタイム中は上下アームとも「オフ」の状態となります。

デッドタイムは、基本的にIGBTのスイッチング時間( $t_{d(off)} + t_f$ )のmax.値より長く設定する必要があります。例えば $R_G$ を大きくすると、スイッチング時間も長くなるのでデッドタイムも長くする必要があります。さらに他の駆動条件や温度特性なども考慮する必要があります。デッドタイムが短い場合、上下アーム短絡が発生して、短絡電流による発熱で素子破壊に至る可能性がありますので注意が必要です。

デッドタイムの設定が良いかどうかを判定する1つの方法として、無負荷時の直流電源ラインの電流を確認することが挙げられます。

図7-6に示す3相インバータの場合、インバータの出力(U、V、W)をオープン状態にして通常の入力信号を与えDCラインの電流を測定します。デッドタイムが十分であっても微小なパルス状電流(素子の出力容量を抜けてくるdv/dt電流: 通常は定格電流の5%程度)が流れますが、デッドタイムが不足していればこれより大きな短絡電流が流れます。この場合、短絡電流が無くなるまでデッドタイムを長くしてください。高温ほどターンオフ時間が長くなることから、この試験は高温状態で実施を推奨します。また、逆バイアス電圧- $V_{GE}$ が不足しても、短絡電流が増加します(第4章3.3項参照)。デッドタイムを増加しても短絡電流が減少しないときには- $V_{GE}$ を増加してください。

図7-5 デッドタイム タイミングチャート

図7-6 デッドタイム不足による短絡電流の検出方法

## 4. ゲート駆動回路設計の具体例

IGBTの用途に応じ、主回路と制御信号回路間を電気的に絶縁する必要があります。このような用途に用いられる高速フォトカプラを使用した駆動回路の例を図7-7に示します。フォトカプラを使用することにより入力信号と素子を電気的に絶縁します。また、フォトカプラは出力パルス幅に対する制約がないので、PWM制御のようにパルス幅が広範囲に変化する用途に適しており、現在では最も広く使用されています。

また、ゲート抵抗を二つ設けてターンオンとターンオフの特性を別々に設定することもできます。

このほか、信号絶縁にパルスransを用いるゲート駆動方法があります。この方法は信号とゲート駆動電力の両方を信号側から同時に供給できるため回路の簡略化が可能です。しかし、オンデューティ比が最大50%、逆バイアスを設定できない、といった制約があります。

図7-7 高速フォトカプラを用いた駆動回路例

## 5. ゲート駆動回路設計、実装上の注意事項

### 5.1 フォトカプラのノイズ耐量について

IGBTは高速スイッチング素子であるため、ゲート駆動回路に使用するフォトカプラはノイズ耐量の大きいものを選定する必要があります。また、誤動作を避けるためフォトカプラの一次側と二次側の配線を交差させないようにしてください。このほか、IGBTの高速スイッチング性能を活かすには信号伝達遅れ時間の短いフォトカプラを使用することを推奨します。

### 5.2 ゲート駆動回路とIGBT間の配線について

ゲート駆動回路とIGBTの間の配線が長い場合、ゲート信号の振動や誘導ノイズによってIGBTが誤動作する可能性があります。この対策として以下の方法があります。

- ・ゲート駆動配線を極力短くする。

- ・ $R_G$ を大きくする。ただしスイッチング時間、スイッチング損失に注意する。

- ・ゲート配線とIGBTの主回路配線は出来る限り遠ざけ、重ねる場合は互いに直交する(相互誘導を受けないように)ようにレイアウトする。

\*<sup>1</sup>  $R_{GE}$ について

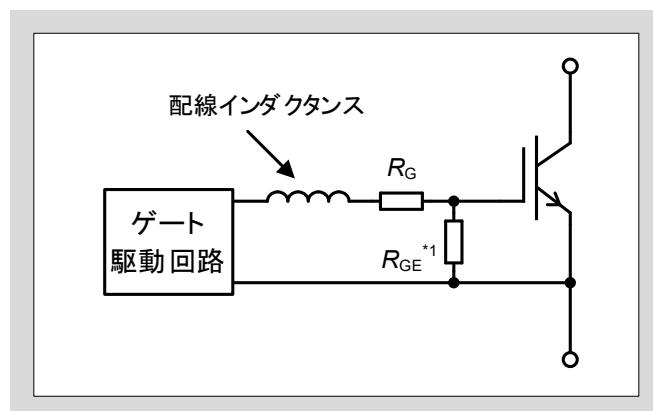

ゲート駆動回路の不具合あるいはゲート駆動回路が完全に動作していない状態(ゲートがオープン状態)<sup>\*2</sup>にて主回路に電圧を印加するとIGBTが破壊することがあります。この破壊を防ぐため、G-E間に10kΩ程度の抵抗 $R_{GE}$ を接続することを推奨します(図7-8参照)。

\*<sup>2</sup>電源投入について

電源投入にはゲート駆動回路電源を投入して完全に動作させた後、主回路電源を投入してください。

図7-8 ゲート駆動回路の実装上の注意

### 5.3 ゲート過電圧保護について

IGBTは他のMOS型素子と同様に十分に静電対策を実施した環境下で取り扱う必要があります。またG-E間最大定格電圧は±20Vです。これ以上の電圧が印加される可能性がある場合には、図7-9に示すようにG-E間にツェナーダイオードやTVSダイオードを接続するなどの保護対策が必要となります。

図7-9 G-E間過電圧保護回路例

## 第8章 ディスクリートIGBTの並列接続

|                   |      |

|-------------------|------|

| 1. ディスクリートIGBTの選定 | 8-2  |

| 2. 主回路の設計         | 8-6  |

| 3. ゲート駆動回路の設計     | 8-8  |

| 4. 放熱設計           | 8-11 |

大電流を制御する回路に適用する際、ディスクリートIGBTを並列接続して使用すると通電電流能力を増大させることができます。しかし、この場合ディスクリートIGBT間の電流アンバランスや温度分布、配線長の増加によるノイズやサージ電圧の増大等を考慮する必要があります。

上記のような問題を防ぐため、並列接続時に留意すべき点は主に以下の4つです。

1. ディスクリートIGBTの選定

2. 主回路の設計

3. ゲートドライブ回路

4. 熱設計

本章では並列接続する際の各留意点の詳細について記載します。

## 1. ディスクリートIGBTの選定

並列接続する際の留意する点として、同一アーム上の各ディスクリートIGBTにおける $V_{CE(sat)}$ のバラツキ( $\Delta V_{CE(sat)}$ )や温度依存性の特性差が挙げられます。この $\Delta V_{CE(sat)}$ 、すなわち各ディスクリートIGBTの出力特性に差が生じることにより、導通時の定常状態において電流アンバランスが発生します。電流アンバランスが過大になると、電流分担の大きいIGBTの発生損失が増大し、熱破壊する可能性があります。したがって並列接続させるディスクリートIGBTを選定する際は $\Delta V_{CE(sat)}$ を留意する必要があります。この考え方は、FWDにおいても同様になります。

### 1.1 $\Delta V_{CE(sat)}$ による電流アンバランスの考え方

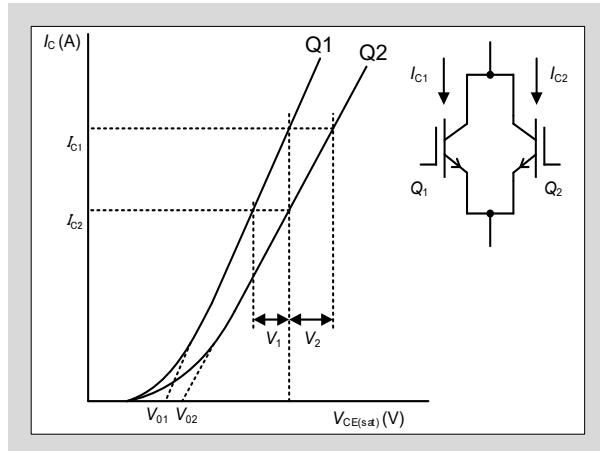

図8-1に異なる $V_{CE(sat)}$ を持つIGBT(Q<sub>1</sub>とQ<sub>2</sub>)の出力特性を示します。Q<sub>1</sub>とQ<sub>2</sub>の $V_{CE(sat)}$ の差を $\Delta V_{CE(sat)}$ とします。図8-1では2並列を例として図示しており、Q<sub>1</sub>とQ<sub>2</sub>の出力特性は以下の式で近似できます。

$$\begin{aligned}V_{CEQ1} &= V_{01} + r_1 \cdot I_{C1} \\r_1 &= V_1 / (I_{C1} - I_{C2}) \\V_{CEQ2} &= V_{02} + r_2 \cdot I_{C2} \\r_2 &= V_2 / (I_{C1} - I_{C2})\end{aligned}$$

したがってQ<sub>1</sub>とQ<sub>2</sub>を並列接続した回路に $I_{Ctotal}(=I_{C1}+I_{C2})$ のコレクタ電流を流した場合、キルヒホッフの法則からQ<sub>1</sub>とQ<sub>2</sub>の電圧が同一になるので、それぞれに流れるIGBTのコレクタ電流は以下のように求めることができます。

$$\begin{aligned}I_{C1} &= (V_{02} - V_{01} + r_2 \cdot I_{Ctotal}) / (r_1 + r_2) \\I_{C2} &= (V_{01} - V_{02} + r_1 \cdot I_{Ctotal}) / (r_1 + r_2)\end{aligned}$$

図8-1 異なる出力特性の組み合わせ例

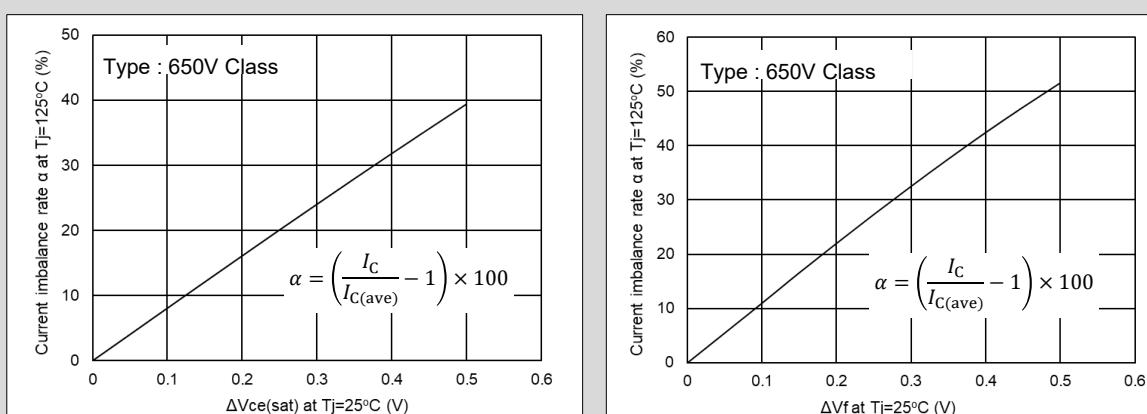

図8-2  $\Delta V$ と電流アンバランス率(左:IGBT、右:FWD)

前述式において $V_{01}=V_{02}$ とした場合、Q<sub>1</sub>にはQ<sub>2</sub>の電流の $r_2/r_1$ 倍の電流が流れることになります。図8-1からわかるように $r_2 > r_1$ であるため、Q<sub>1</sub>の電流分担が大きくなります。このように $\Delta V_{CE(sat)}$ がある場合には $V_{CE(sat)}$ が低い方のIGBTの電流分担が大きくなります。

この並列接続時に生じる電流分担の割合は電流アンバランス率と呼ばれ、各IGBTの $\Delta V_{CE(sat)}$ によって決定されます。図8-2に、2並列接続させたXSシリーズディスクリートIGBTの $\Delta V_{CE(sat)}$ と電流アンバランス率の関係を示します。 $\Delta V_{CE(sat)}$ が大きくなると電流アンバランス率が大きくなることが分かります。したがって並列接続をする際には $\Delta V_{CE(sat)}$ が小さい製品を組み合わせることが重要となります。

## 1.2 $\Delta V_{CE(sat)}$ の最小化

良好な電流分担を得るために $\Delta V_{CE(sat)}$ の小さいIGBTを組み合わせる必要があります。 $\Delta V_{CE(sat)}$ は同一製品ロットのディスクリートIGBTを用いることにより最小にすることができます。これは原料のバラツキや製造・検査工程から生じる影響を最小にできるためです。したがって並列接続を行う場合、同一製品型式の同一製品ロットを使用してください。

## 1.3 出力特性の接合温度 $T_{vj}$ 依存性と電流アンバランス

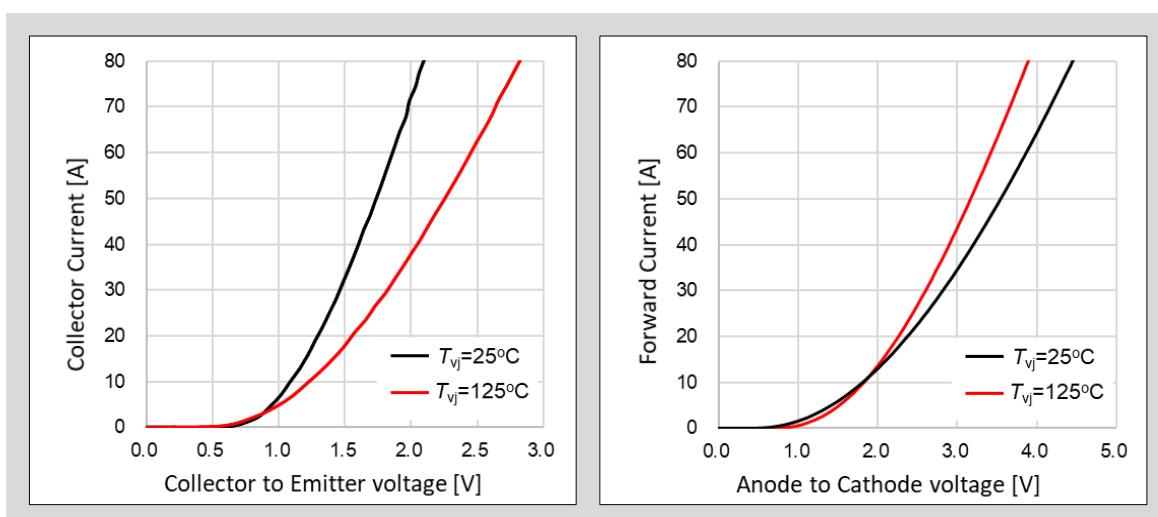

IGBTやFWDの出力特性は接合温度 $T_{vj}$ 依存性を有しており、並列接続されたディスクリートIGBTの電流アンバランスに影響を与えることがあります。並列接続を行う際は留意する必要があります。ここでは40A定格のXSシリーズディスクリートIGBTを例として、図8-3にIGBTとFWDの出力特性を示します。

本章1.1で述べたように、 $\Delta V_{CE(sat)}$ があるIGBTを2並列接続した時、 $V_{CE(sat)}$ の低いIGBTの電流分担が大きくなります。これにより $V_{CE(sat)}$ の低いIGBTの発生損失が大きくなり、 $T_{vj}$ はもう一方よりも上昇します。IGBTは正の温度特性を有するため、 $T_{vj}$ が上昇するにつれて $V_{CE(sat)}$ が高くなるので、それに伴い電流分担は小さくなります。このように、IGBTの並列接続の場合では、温度上昇によって並列接続された双方のIGBTに流れる電流がバランスしあう方向に作用します。

一方で、FWDは負の温度特性を有するため、 $\Delta V_F$ があるFWDを2並列接続した時、 $T_{vj}$ の上昇に伴い $V_F$ が低くなるので、それに伴い電流アンバランスを増長する方向に作用します。

従って、IGBTやFWDを並列接続する場合、 $T_{vj}$ の上昇によって電流アンバランス率に影響を及ぼします。図8-2に記載の電流アンバランス率はこの現象を考慮していますので、FWDのアンバランス率の方が大きくなっています。

図8-3 出力特性比較(左:IGBT、右:FWD)

## 1.4 多並列接続時のディレーティング

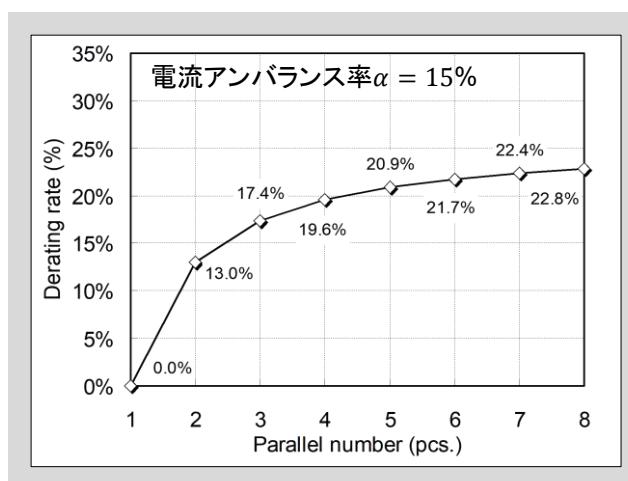

IGBTの並列接続時には電流アンバランスを考慮する必要があり、その電流総和(流すことができる最大電流)は定格電流の総和に対するディレーティング(電流低減)が必要となります。n個の素子を並列接続する場合、最も $V_{CE(sat)}$ が低い1素子への電流集中が最悪条件と考えます。n個の素子を並列接続した場合の許容最大電流 $\Sigma I$ は、2並列時の電流アンバランス率 $\alpha$ を用いて以下の式で表すことができます。

$$\sum I = I_{C(\max)} \left[ 1 + (n - 1) \frac{\left(1 - \frac{\alpha}{100}\right)}{\left(1 + \frac{\alpha}{100}\right)} \right] \quad \alpha = \left( \frac{I_{C1}}{I_{C(\text{ave})}} - 1 \right) \cdot 100$$

ここで上式の電流アンバランス率 $\alpha$ は図8-1に示した2並列時の電流値 $I_{C1}$ と平均電流値 $I_{C(\text{ave})}=(I_{C1}+I_{C2})/2$ により求められます。また $I_{C(\max)}$ は1素子当りの最大電流、 $\Sigma I$ は並列接続時の最大電流を表しています。この $\Sigma I$ を流すためには並列接続した全ての素子が仕様書に記載のRBSOAを満足する必要があるとともに、発生損失によって生じる接合温度の上昇を $T_{vj(max)}$ 以下にする必要があります。特に発生損失による接合温度の上昇は使用条件(スイッチング周波数、ゲート駆動条件、放熱条件、スナバ条件等)により異なるので注意が必要です。

たとえば $\alpha=15\%$ 、 $I_{C(\max)}=40A$ 、 $n=4$ の場合では $\Sigma I \approx 128.7$ となり単純に $40 \times 4 = 160A$ とはならず約19.6%のディレーティングが必要であることがわかります。このように並列時の全電流 $\Sigma I$ は、単純な電流総和( $n \times I_{C(\max)}$ )に対してディレーティングが必要となります。

電流アンバランス率 $\alpha=15\%$ とした場合のIGBTのディレーティング率を図8-4に示します。この図からわかるように、並列数の増加とともにディレーティング率が大きくなっています。したがって並列接続を行う際、接続数に応じたディレーティングを行ってください。またディレーティング率は電流アンバランス率によって異なりますので、注意してください。

本例に示すディレーティング率は前記の電流アンバランス率から求めた参考値ですので、実機動作によってアンバランス確認と検証を行った上でディレーティング率を決定してください。

図8-4 並列接続数とディレーティング率の関係

## 2. 主回路の設計

並列接続された各ディスクリートIGBT間の主回路配線におけるバラツキは、定常動作とスイッチング動作時の電流アンバランスに大きな影響を与えます。これは誤動作の誘因になる可能性があるため、並列接続の主回路設計を行う際は主に次の2点を留意し、主回路を均等かつ短く設計する必要があります。

- (1) 主回路配線抵抗のバラツキ

- (2) 主回路配線インダクタンスのバラツキ

### 2.1 主回路配線抵抗のバラツキ

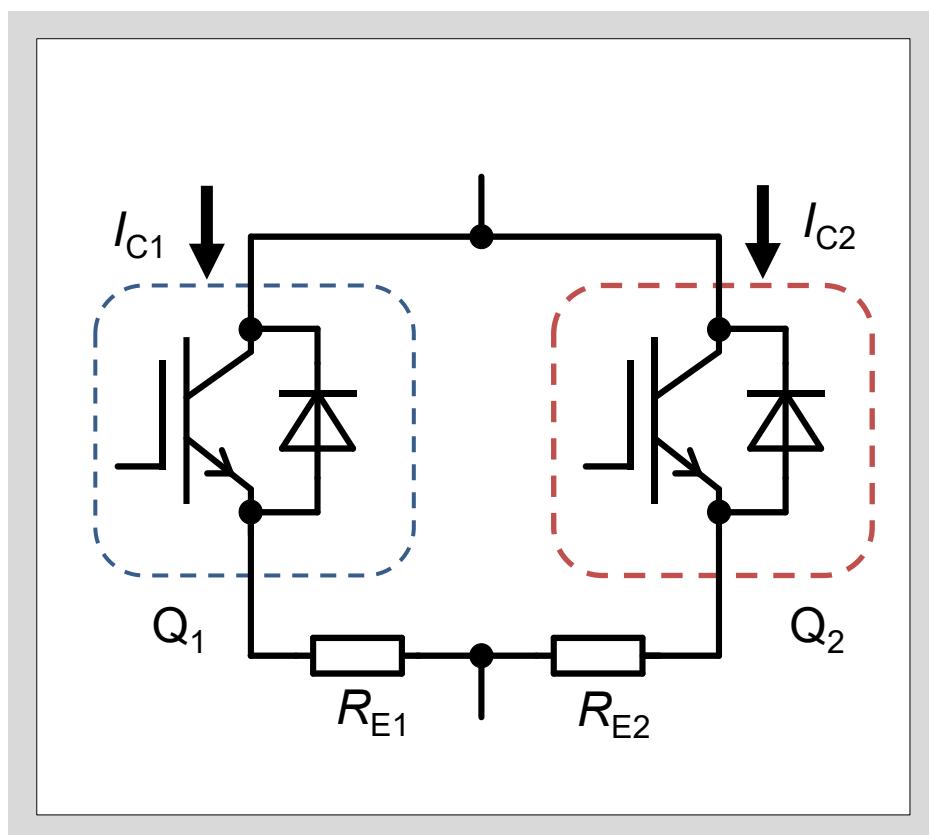

図8-5に主回路配線抵抗を示した2並列接続時の簡易等価回路を示します。ここではコレクタ側の抵抗成分を省略して記載しています。

この主回路配線の抵抗成分が大きい場合、抵抗成分が小さい場合と比べ、オームの法則に従い $Q_1$ と $Q_2$ に流れるコレクタ電流の合計は減少し、この抵抗成分が大きい程、コレクタ電流の合計は小さくなります。

さらに主回路配線の左右で抵抗に不均等があり、 $R_{E1} > R_{E2}$ と仮定した場合、 $I_{C1} < I_{C2}$ となり、 $Q_1$ と $Q_2$ で電流アンバランスが生じます。

このように主回路の抵抗成分によって、コレクタ電流の減少や電流アンバランスが発生する可能性があります。したがってこの影響を低減するためには、エミッタ側の配線は極力短くかつ均等にする必要があります。

図8-5 主回路配線に抵抗成分がある場合の等価回路図

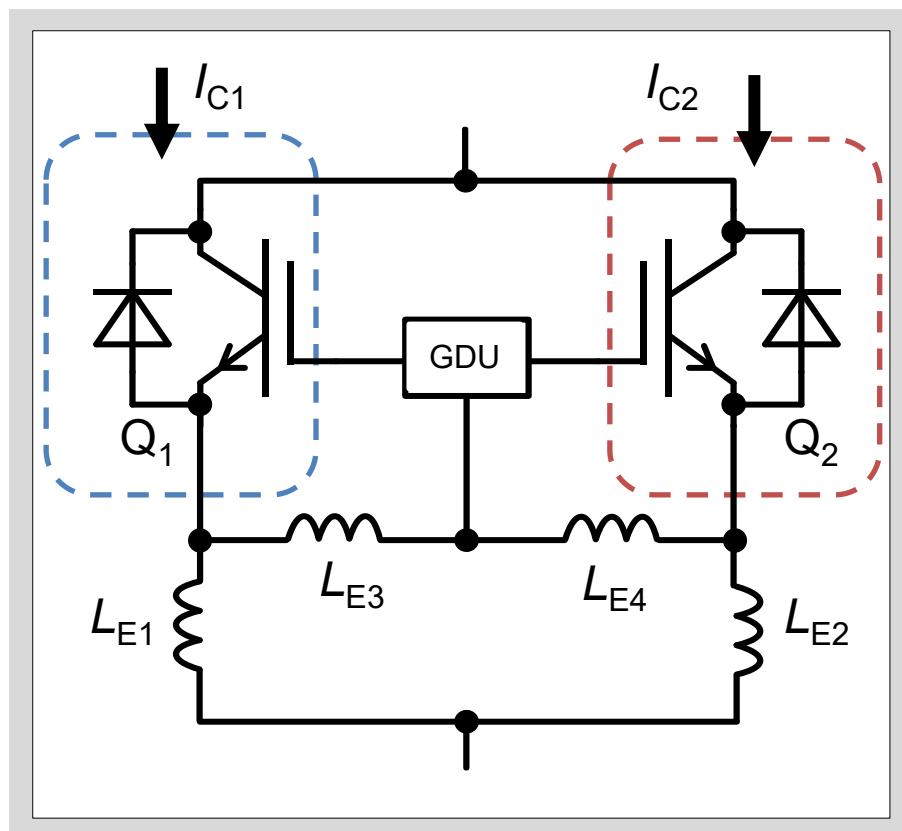

## 2.2 主回路配線インダクタンスのバラツキ

図8-6に主回路配線インダクタンスを示した2並列接続時の簡易等価回路を示します。主回路配線のインダクタンスが左右で不均等の場合、並列接続した各IGBTのスイッチング時の電流分担にアンバランスが生じます。 $Q_1$ と $Q_2$ のIGBTに流れるコレクタ電流をそれぞれ $I_{C1}$ 、 $I_{C2}$ としたとき、電流分担は各IGBTの配線インダクタンス $L_{E1}$ と $L_{E2}$ の差に影響を受け、ほぼインダクタンス比によって決まります。したがってスイッチング時の電流アンバランスを緩和するためには配線インダクタンス長をできる限り均等にすることが必要です。 $L_{E1}$ と $L_{E2}$ の配線インダクタンスが異なる場合、ターンオン時の電流の時間的変化( $di/dt$ )によって発生する $L_{E1}$ と $L_{E2}$ の誘起電圧に差が生じます。誘起電圧の差は並列接続した各IGBTの実効的に印加されるゲート電圧に影響を与え、電流アンバランスを助長します。このことから、並列接続を行う際、主回路配線は可能な限り $L_{E1}=L_{E2}$ となる配線にすることが重要となります。また、主回路配線インダクタンスが大きいとIGBTターンオフ時のサーボ電圧が大きくなるため、配線インダクタンスはできる限り小さくする必要があります。

図8-6 主回路配線インダクタンスを考慮した並列接続時の簡易等価回路

### 3. ゲート駆動回路の設計

ディスクリートIGBTの並列接続におけるゲート駆動回路の設計方法には、第4章の内容に加え並列接続時特有の留意点があります。また、これは並列接続時のゲートドライバ構成によって留意すべき点が異なります。この留意点を考慮しない場合、ゲート駆動回路が原因で電流アンバランスや誤動作が発生し、ディスクリートIGBTが破壊する可能性があります。下記では並列接続におけるゲート駆動回路設計時に留意すべき主な点を説明します。

#### 3.1 ゲート駆動回路とゲート - エミッタ端子の接続方法

並列駆動させる際、ディスクリートIGBTに補助エミッタ端子がある場合は、補助エミッタ端子を用いてゲート駆動してください。補助エミッタ端子がない場合にゲート駆動回路のエミッタ配線を、図8-6に示した配線インダクタンス $L_{E1}$ と $L_{E2}$ が不均衡となるような位置に接続すると、スイッチング時の各ディスクリートIGBTのゲート電圧挙動に差異が発生し、過渡的な電流分担がアンバランスになります。TO-247-4パッケージにはゲート駆動回路用に補助エミッタ端子を設けており、この端子を使用すれば、 $L_{E1}$ と $L_{E2}$ が均等になるので、過渡的な電流アンバランスを抑制することができます。

しかし補助エミッタ端子を用いてゲートを駆動した場合でも、ゲート駆動回路から各ディスクリートIGBTまでのエミッタ配線が長く、不均等になれば電流アンバランスを引き起こします。したがって並列接続した各ディスクリートIGBTへのゲート駆動回路の配線は均等な長さで最短かつ対称となるように設計してください。このとき、ゲート駆動回路の配線は主回路配線からはできるだけ遠ざけ平行にならないようにし、相互誘導(特にコレクタ電流)を受けないように配置してください。

#### 3.2 並列接続時のゲート駆動回路の留意点

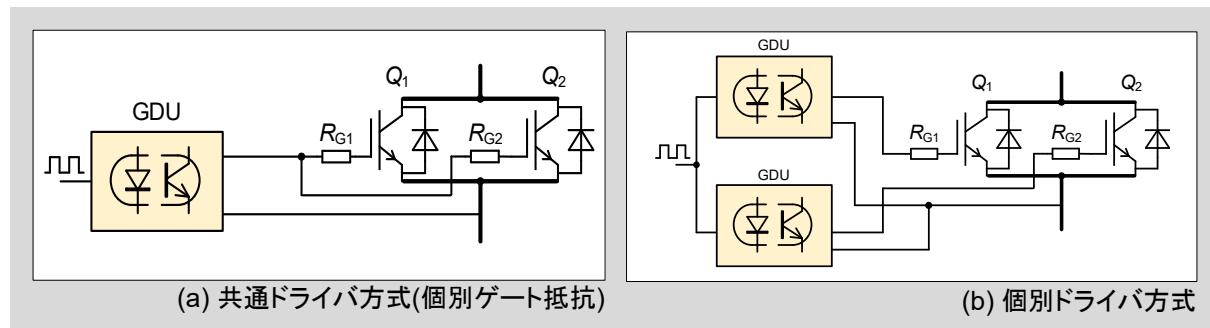

ディスクリートIGBTの並列接続におけるゲート駆動回路の方式は、多岐にわたり、ゲートドライバ構成によって留意すべき点が異なります。並列接続におけるゲート駆動回路の構成例として、図8-7(a)に共通ドライバ方式(1つのゲート駆動回路で並列接続された各ディスクリートIGBTを動作させる構成)を示し、図8-7(b)に個別ドライバ方式(並列数分のゲート駆動回路で各ディスクリートIGBTを動作させる構成)を示します。以降のページでは、この代表的な2つのゲート駆動回路の方式の詳細とその設計時の留意点について説明します。

図8-7 並列接続時のドライバ構成

### 3.2.1 並列駆動における共通ドライバ方式について

共通ドライバ方式の特性として、並列接続されたディスクリートIGBTを駆動させる電源やフォトカプラを共通に出来るため、ゲート駆動回路を簡素化でき部品点数を少なくすることが挙げられます。一方で、並列接続された複数のディスクリートIGBTを単一の電源で駆動させるため、電源容量を大きくする必要があります。

また、並列接続された各ディスクリートIGBTのエミッタ部がゲート駆動回路内部で共通になり閉ループが出来るので、スイッチング時にゲート電圧の変動が誘起され、IGBTが誤動作する可能性があります。実例として寄生振動を起こしたターンオン波形を図8-8に示し、寄生振動の発生メカニズムを下記に示します。図8-8の $L_{E1}$ と $L_{E2}$ にバラツキがある場合、配線インダクタンス差とIGBTの入力容量により横流が発生し、 $L_{E3}$ と $L_{E4}$ に起電力が発生することで、ゲート電圧が寄生振動することがあります。

共通ドライバ方式の駆動回路を使用する際は、ゲート回路にコモンモードチョークコイルやエミッタ側に抵抗 $R_E$ を挿入するなどの対策を検討し、上記の問題が発生しないことを確認してください。

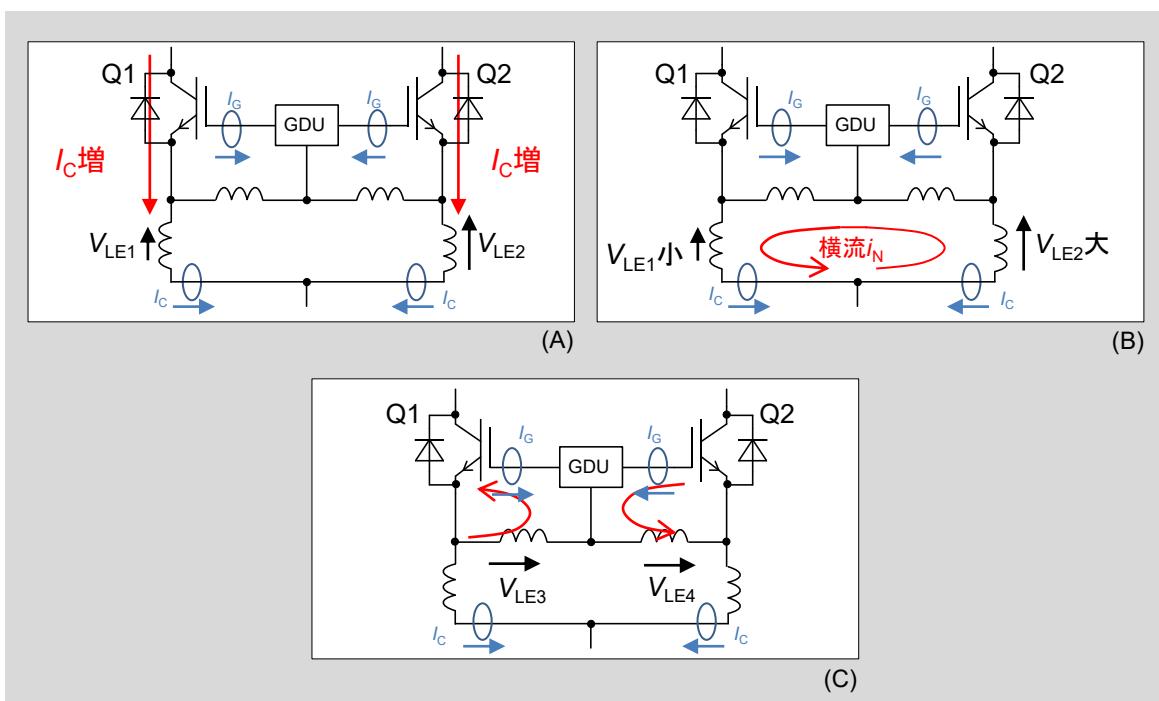

#### 共通ドライバ方式におけるターンオン時の寄生振動メカニズム

- (A)  $Q_1$ と $Q_2$ のIGBTがターンオンすることにより、 $I_C$ が増加し主回路に $dI/dt$ が発生する。これにより配線インダクタンスに起電力 $V_{LE1}$ 、 $V_{LE2}$ が発生する。

- (B) 配線インダクタンスに差がある時、起電力 $V_{LE1}$ と $V_{LE2}$ の大きさに差異があるので、閉ループに横流 $i_N$ が発生する。

- (C) 横流 $i_N$ によりGDU-エミッタ間の配線インダクタンス $L_{E3}$ と $L_{E4}$ に起電力 $V_{LE3}$ と $V_{LE4}$ が発生し、これにより $Q_1$ と $Q_2$ への充放電電流によりゲート電圧の寄生振動が発生する。

図8-8 寄生振動メカニズム

### 3.2.2 並列駆動における個別ゲート駆動回路について

個別ドライバ方式の特長として、並列接続された各ディスクリートIGBTのエミッタ部が共通にならず閉ループが出来ないので、エミッタ部に横流が発生せず、図8-8で示した寄生振動のような誤動作リスクが減ります。一方で、並列接続されたディスクリートIGBTに対し個別のゲート駆動回路を配置するためゲート駆動回路が複雑化します。また、ゲート駆動回路に搭載されるフォトカプラなどの電子部品の特性バラツキによって、並列接続された各ディスクリートIGBTにオン/オフのタイミング差が発生し、スイッチング時に電流アンバランスもしくは誤動作の可能性が生じます。したがって、個別ドライバ方式のゲート駆動回路を設計する際は、各ディスクリートIGBTのオン/オフのタイミング差を限りなく小さくする必要があるため、電子部品の特性ばらつきを考慮してください。

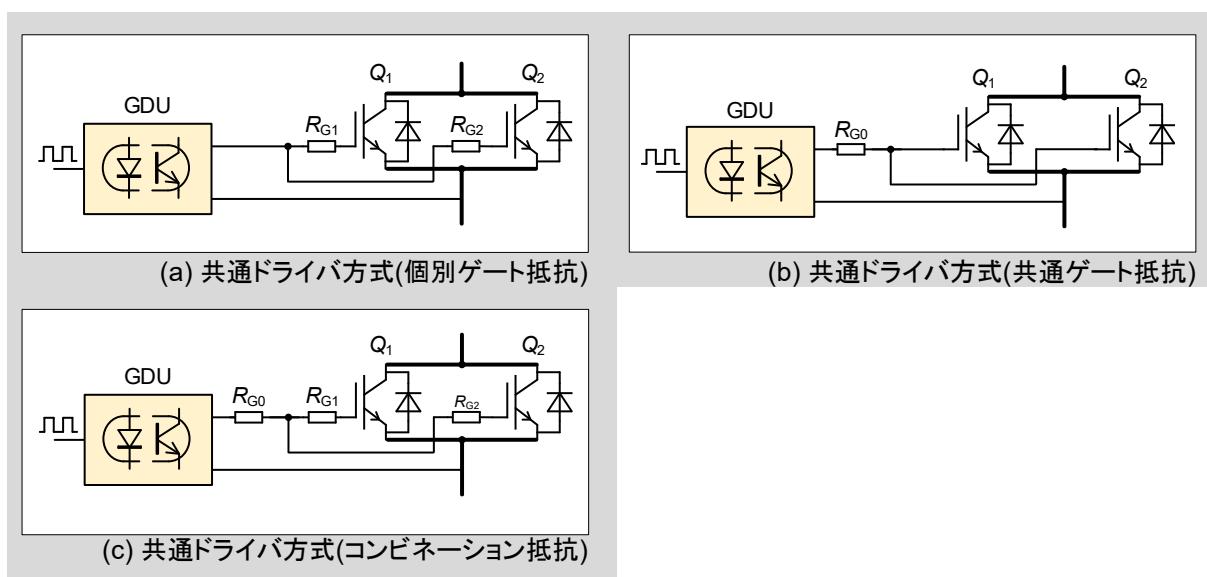

### 3.2.3 共通ドライバ方式におけるゲート抵抗の接続方法

並列接続時に共通ドライバ方式で構成する場合のゲート抵抗の構成は図8-9に示す様に3つの方式があります。

(a)の個別ゲート抵抗方式の場合、各ディスクリートIGBTに接続されているゲート抵抗により、ゲート回路配線の回路インダクタンスとIGBTの入力容量による寄生振動を抑制することができます。しかし、各ディスクリートIGBTを同一のドライバICに接続しても、各ゲート抵抗のバラツキにより、スイッチング時の各IGBTのオン/オフのタイミング差が大きくなることがあります。電流アンバランスや誤動作の可能性があります。

(b)の共通ゲート抵抗方式の場合、各ゲート抵抗値の差がなくなるので、各IGBTのオン/オフのタイミング差を最小にすることが出来ます。しかし、ゲート回路配線の回路インダクタンスとIGBTの入力容量のLC共振により、ゲート電圧の立ち上がり時に寄生振動を起こす場合がありますので注意が必要です。

電圧の寄生振動やIGBTのオン/オフのタイミング差が生じないことを確認すれば、共通ゲート抵抗方式もしくは個別ゲート抵抗方式の適用は可能です。しかし、新規でドライバ回路を設計する場合は、双方の特長を備えた共通ゲート抵抗方式と個別ゲート抵抗方式を組み合わせた(c)のコンビネーションゲート抵抗方式を適用することを推奨します。

図8-9 共通ドライバ方式におけるゲート抵抗の接続方法

## 4. 放熱設計