ニュースリリース

『Super J-MOSシリーズ』の発売について

2011年12月22日

富士電機株式会社

富士電機株式会社(東京都品川区、代表取締役社長:北澤通宏)は、業界最高レベルの低損失を実現したMOSFET『Super J-MOSシリーズ』を発売しますのでお知らせ致します。

1.発売のねらい

地球環境への関心が高まる中、グリーン化が進むIT分野や新エネルギー分野などでは電力変換の効率化を実現するパワー半導体に注目が集まっています。

その中でも、MOSFET(注1)は、電力変換に使用される主力デバイスとして、これまで以上の損失改善が求められています。

このたび、当社が発売する『Super J-MOSシリーズ』は、新たに開発した低オン抵抗特性を持つSJ構造(注2)を採用し、大幅な損失低減を可能としました。

これにより、機器の電力変換効率を向上させ、消費電力を減らすことで、低炭素社会の実現に貢献します。

2.製品の特長

-

オン抵抗70%(注3)減を実現し、業界最高レベルの低損失を達成

-

最新のスイッチング損失低減技術と組み合わせ、素子のトータル損失14%低減(注4)

3.概略仕様(代表機種)

4.主な用途

-

サーバー、無停電電源装置、放送機器などの情報通信機器

-

太陽光パワーコンディショナーなど新エネルギー分野向け電力変換装置など

-

(注1)

-

MOSFET:Metal-Oxide-Semiconductor Field-Effect Transistor

-

(注2)

-

SJ構造:Superjunction構造

-

-

MOSFETのドリフト層をp型領域とn型領域とが交互に並んだ構造に置き換えたもので、n型領域の不純物濃度を高くすることができ、抵抗値を劇的に低減できるのが特長です。

従来のプレーナー構造のMOSFETでは、高抵抗のn型層に電気的に絶縁された領域(空乏層)を伸ばすことによって耐圧を確保していたため、オン抵抗を一定値以下には出来ませんでした。

SJ構造は、n型領域にp型領域を形成することで、縦方向だけでなく横方向にも空乏層を伸ばすことが出来るため、n型層の抵抗を下げても耐圧が確保されます。これにより、従来のプレーナー構造の理論限界を超えた低オン抵抗を実現しています。

-

(注3)、(注4)

-

当社従来製品との比較です

SJ構造参考図

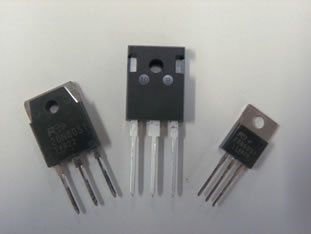

Super J-MOS製品写真

【お客様問合せ先】

富士電機株式会社 営業本部 パワエレ機器統括本部

第3統括部 営業第1部

tel:03-5435-7256

以上